Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

Hello,

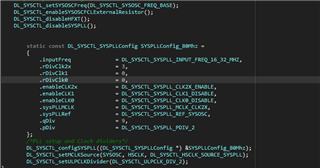

Clock sysconfig configuration:

1. Explanation of the Issue:

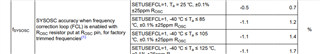

a. I am using the internal system oscillator (SYSOSC) at 80 MHz on the MSPM0G1507 and have configured a PWM with a period count for 2 kHz. However, I am observing unexpected frequency variations in the output waveform:

Single Initialization: The measured PWM frequency is 2025 Hz, which is higher than the expected 2000 Hz. This deviation suggests a high frequency tolerance issue.

Double Initialization (Calling Initialization Function Twice): The output frequency is now in the range of 2005-2015 Hz, which is much closer to the expected value.

Is it expected that MSPM0G1507 requires re-initialization to correct this issue, or is there an alternative way to ensure accurate PWM frequency on the first initialization?

2. Issue with FCL Application:

a. I tested logic and found that the DL_SYSCTL_enableSYSOSCFCLExternalResistor() function plays a major role in clock tolerance.

If I remove this function, I consistently get an out-of-tolerance frequency, around 2030 Hz (exceeding the 2020 ±20 Hz limit).

Even with two initializations, I still observe the same out-of-tolerance frequency.

b. When using DL_SYSCTL_enableSYSOSCFCLExternalResistor() for FCL, I still see inconsistent results:

i.On the first initialization, the frequency is 2025 Hz.

ii.On the second initialization, the frequency drops to around 2003 Hz.

This raises a doubt: Is FCL not applied during the first initialization but only on the second one? (Note: The FCL mode is enabled on the first attempt itself.)