Part Number: AM2634

Tool/software:

Dear TI team,

I am using the AM2634 and MCAL software, and I have encountered the following issues that I would like to ask about.

1. Does TI provide an MCAL demo project?

Currently, the MCAL_AM263X_10.00.00.zip provided by TI does not contain an MCAL demo project.

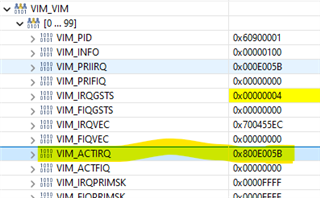

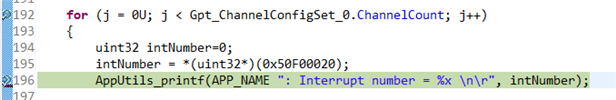

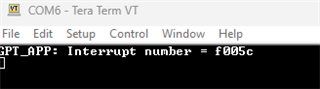

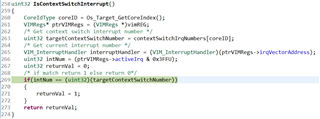

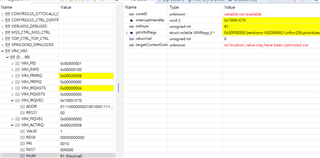

2. Reading the interrupt number of the currently executing register

When using the TI AM263x, it is not possible to directly read the interrupt number of the currently executing interrupt through the register. Instead, it is necessary to first read another register (which stores the address of the currently executing interrupt handler) and then read the original register to obtain the interrupt number. I'm unsure whether this approach is considered a workaround.

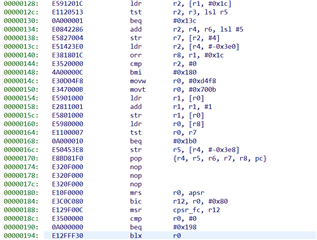

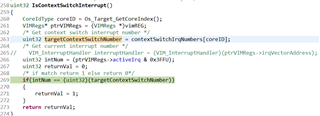

/* Get current interrupt number */ VIM_InterruptHandler interruptHandler = (VIM_InterruptHandler)(ptrVIMRegs->irqVectorAddress); uint32 intNum = (ptrVIMRegs->activeIrq & 0x3FFU);

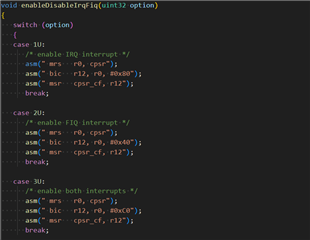

3. Issues encountered when using sys_vim.c in the demo code

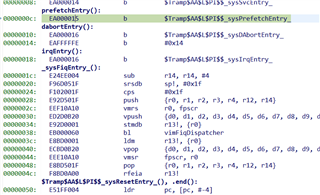

The MCAL provided by TI includes a VIM (Vector Interrupt Manager) demo code, which uses assembly language to enable and disable interrupts(enableDisableIrqFiq). However, when compiler optimization is enabled, this assembly code causes a trap. This seems to be a bug in the demo code. Does TI have an updated version of this demo code?

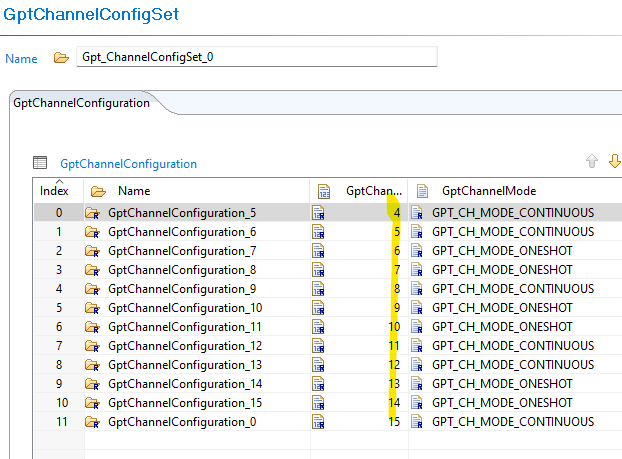

4. How to calculate the GPT timer interrupt interval

Currently, we are using the GPT timer, which is driven by the RTI module. The RTI module has a clock source that is divided based on ClockDivId, and the resulting frequency becomes the actual RTI frequency. All these configurations are set up through EB.

At runtime, we can configure how often the RTI triggers an event, and each event triggers the GPT timer once. The function StartTime() can be called at runtime to set the interrupt interval.

However, the calculated interrupt interval does not match the measured result.

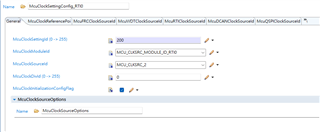

Current EB settings:

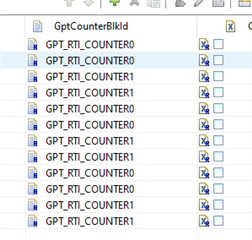

-

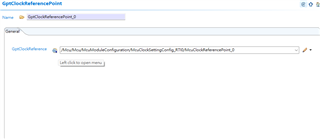

The GPT timer references

McuClockSettingConfig_RTI0'sMcuClockReferencePoint_0(Figure 1). -

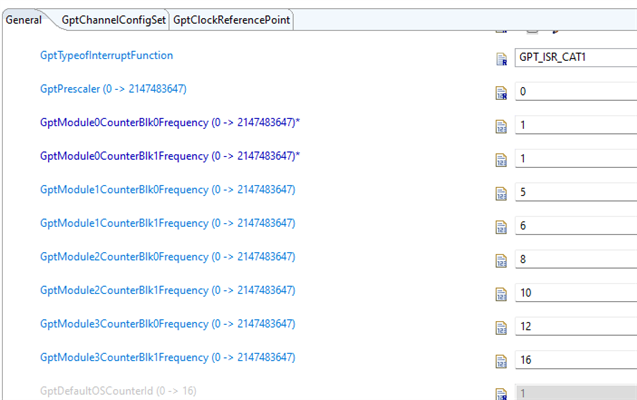

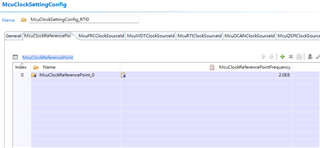

McuClockReferencePoint_0frequency is 2E8 (Figure 2). -

The clock divider is 0 (Figure 3).

Figure 1

Figure 2

Figure 3

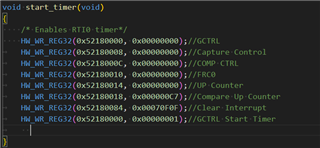

Runtime settings:

-

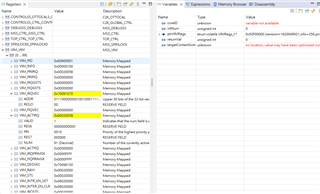

Compare up counter 1 is set to 199 (Figure 4), meaning an event is triggered every 200 cycles.

-

This means 2E8 / 200 = 1E6, approximately 1 microsecond per event.

-

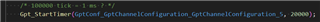

Figure 5 shows that the GPT timer is started, and an interrupt occurs every 20,000 events, meaning it should be triggered every 1 microsecond × 20,000 = 20ms.

-

However, using TSMASTER, the actual measured interrupt interval is 0.2ms, which is 100 times shorter than expected.

Figure 4

Figure 5

These are my questions, and I look forward to your response.

Thanks.

Best Regards,

ph tseng

Figure 2

Figure 2

Figure 4

Figure 4

Figure 3

Figure 3 Figure 4

Figure 4