Part Number: AM6442

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

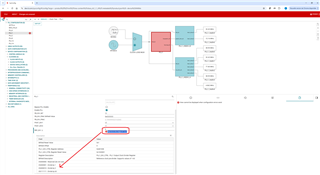

The tool is detecting an invalid error, explaning the range of the acceptable data is [1;63] and refusing the value "5"

The value 5 is used in EVM board, so I am sure that it is a valid configuration

I propose you a correction of the json file used for the description in the tool

Please update the tool in a new version, based on this change, as the generation of files is blocked when an error is detected

On my setup, the file modified is "C:\ti\sysconfig_1.22.0\dist\deviceData\AM64x\clocktree.json"

...I will include the file in next message, as blocking the creation of the ticket for now...