Other Parts Discussed in Thread: SYSCONFIG,

Tool/software:

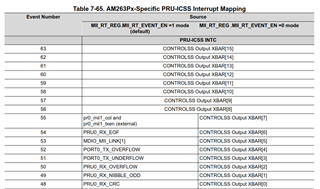

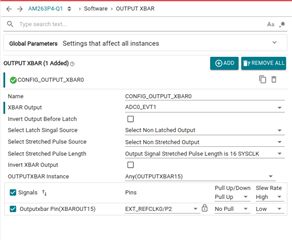

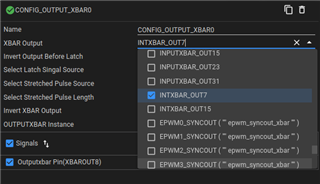

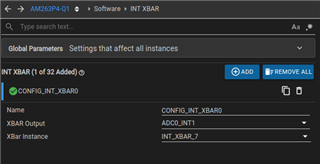

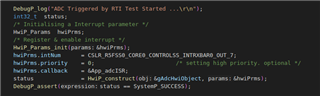

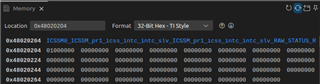

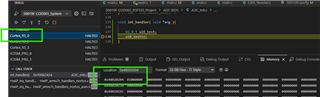

I am looking to use the XBAR to trigger an interrupt on PRU_0 when ADC0 has Interrupt 1 trigger. I am trying to do this mostly through SysConfig on R5FSS0, but I assume there are several lines that need to be added into the PRU_0 code. Both the R5FSS0 and PRU_0 code are written in c.

I'm still reading through documentation, but it looks like I can use the Output XBAR to map the ADC event to the ICSS (PRU and ICSS are seemingly interchangeable in the documentation). In SysConfig, its quite unclear how to correctly configure the Output XBAR for this. I can easily figure out the XBAR instance I added is having its input event selected as well as several other parameters. But how its configuring the instance of the XBAR that will be used and any associated signals isn't very clear.