Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi MSP team,

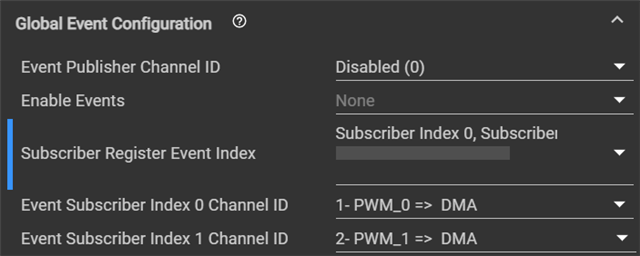

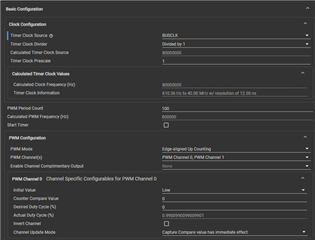

I've got some questions regarding TIMx event for PWM and DMA transfer mode.

1) one FSUB_x register can be shared with 7ch of PWM?

- Period: 1.25us

- PWM channel needed: 5-7ch

- Need to change duty per cycle

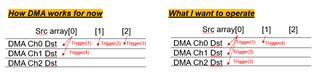

- There're two patterns of duty, and it comes out randomly (stored in DMA)

- Used DMA -> GEN CHAN -> TIMx to set the duty value (not using CPU interrupt)

- There're two FSUB channels for subscribing value from DMA, but it needs to control up to 7 channels.

-> It has been implemented for using one channel (FSUB_0), but customer needs to confirm whether other PWM channels also can use the same FSUB_0.

Actually, I couldn't fully understand what FSUB_x registers are, and how the event works with GEN CHANs. Could you please explain this and confirm the questions from customer?

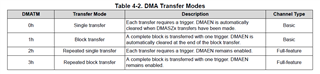

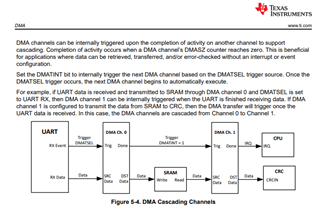

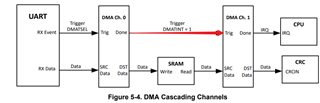

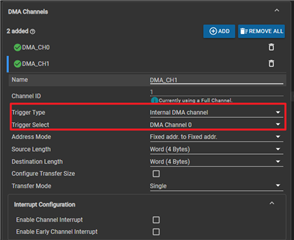

2) DMA trigger mode

- they made buffer with data for changing duty

- When DMA triggered, they would like to send the buffer data, and make it stop when the last data from buffer is finally sent.

In this case, which mode is most fit? and could you explain what is happening and the difference in each the single transfer and repeated single transfer mode?

I think the single transfer works for this case, could you confirm it please?

I also wonder what each DAMSA, DMADA, and DMASZ mean, and how it works.

Thank you for your help in advance.

Many thanks,

Yesol