Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello,

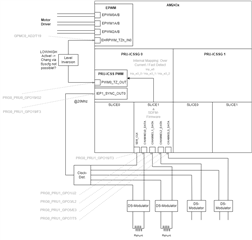

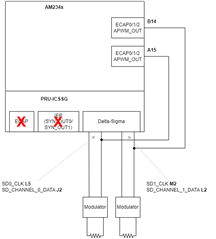

my question is related to clock generation for the delta-sigma filter modulators located in the PRU-ICSSG. Normally, and as i saw in examples provided by TI, the internal ECAP APWM_OUT or IEP SYN_OUT0/1 are used for this task as well SD8_CLK is used as common clock input. However, since on my hardware i cannout use the internal ECAP or IEP for clock generation, my plan is to use the "general" ECAP modules as showen in the following picture:

(The SDFM Firmware should run in PRU1 Core on ICSSG0)

My main question is, if this is possible? If its possible, my next question what must be configured in sysconfig - What bothers me is that "SDFM Clock Configuration" requires a value for "ChannelX SDFM Clock (Hz)" - Why there has to be defined a value since the CLK is provided externally?

Thanks,

Christian