Part Number: MSPM0G3107

Tool/software:

Hello,

I am testing MSPM0G350x.

How many clocks cost to access each register from CPU? ALL register is 1 CPU clocks?

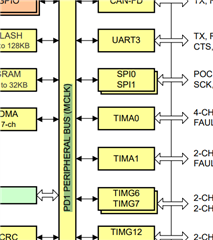

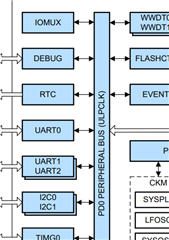

Or Is it depends on peripheral side bus clock? (such as IOMUX register = ULPCLK, UART3 = MCLK)

Thanks,

GR