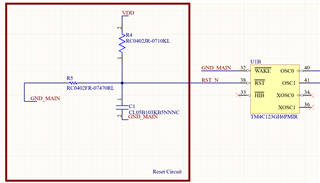

Part Number: TM4C123GH6PM

Other Parts Discussed in Thread: EK-TM4C1294XL

Tool/software:

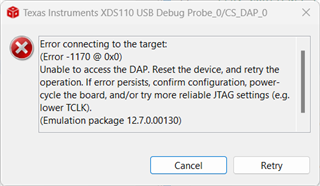

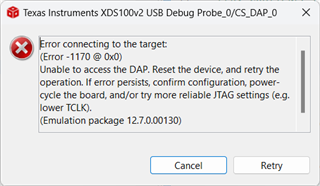

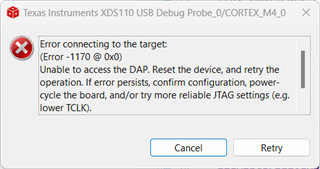

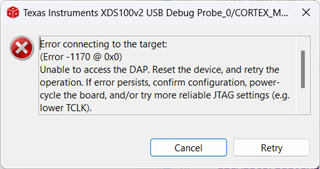

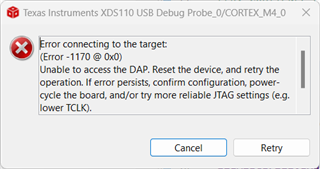

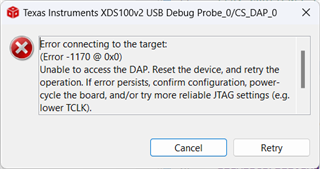

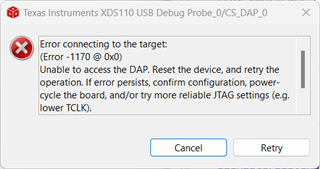

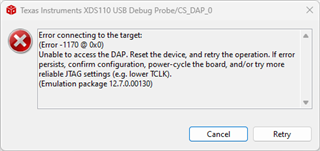

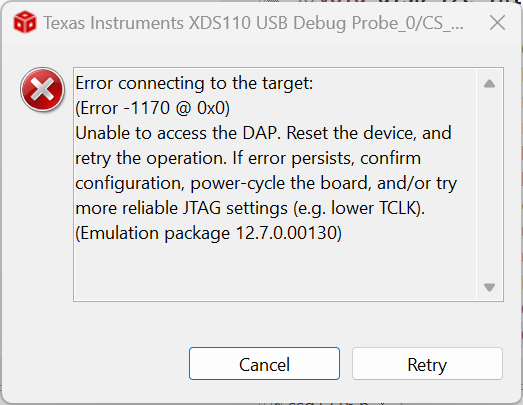

I am having trouble programming a TM4C123GH6PM on a custom board. I keep getting the following error message,

I have tried resetting the DAP using dbgjtag.exe but this has not worked.

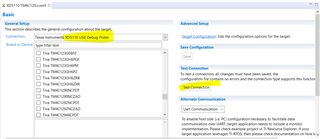

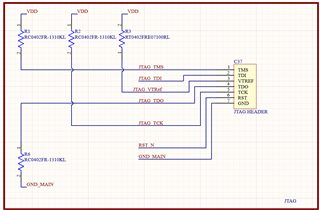

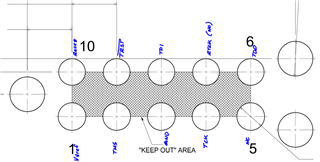

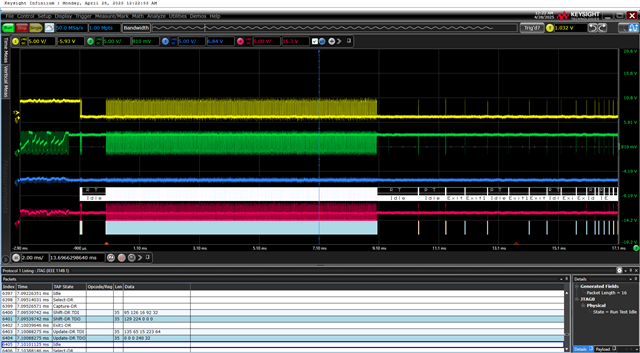

Below is a screenshot of the JTAG header,

Channel 1 TMS, Channel 2 TCK, Channel 3 TDI, Channel 4 TDO.

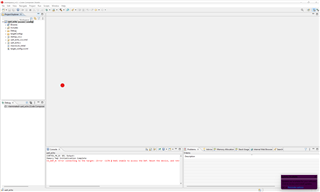

Data from a protocol decode is attached.

Thanks,

AllanDAP.csv