Part Number: AM2612

Other Parts Discussed in Thread: SYSCONFIG, LP-AM263, , UNIFLASH

Tool/software:

Hi all:

I am currently working with the LP-AM2612 to debug the ospi_flash_dma example and encountered an issue requiring your expertise. Here are the details:

-

Original JSON Issue

-

Generated a device configuration JSON using the

ospi_flash_diagdiagnostic example. -

Attempted to import the JSON into CCS v20, but the import process hangs indefinitely (continuously "spinning").

-

-

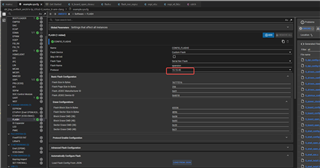

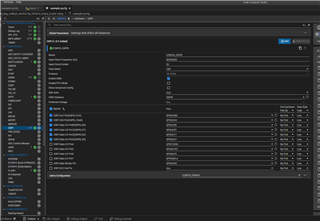

Manual Configuration Attempt

-

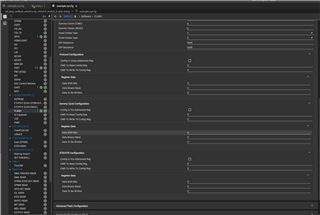

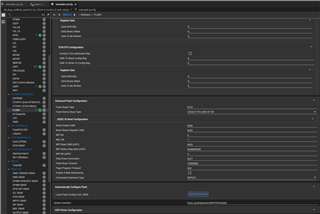

Proceeded to manually configure the OSPI Flash parameters based on the JSON content.

-

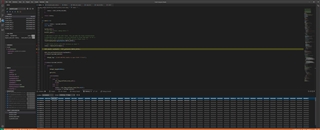

However, during debugging, no signal activity is observed on the OSPI interface (confirmed via logic analyzer).

-

Request:

Could you please:

-

Verify if the

ospi_flash_diagJSON generation/import process is compatible with CCS v20?

- Provide a validated OSPI Flash configuration on syscfg for the LP-AM2612?

Best regards

zx