Tool/software:

Dear TI experts,

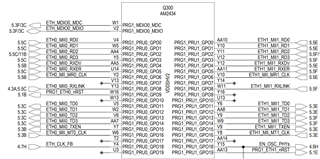

we are trying to establish an EtherCAT connection to a custom board with an AM2434 µC and two DP83822 PHYs (addresses 0 and 1). For testing purposes we are also running the software on the AM243 LaunchPad. Our software is based in on the TIDEP Dual Motor Drive example from the AM243 MotorControlSDK.

With the LaunchPad we are able to connect to the device over EtherCAT using the TwinCAT software on both Ethernet ports. For our own board we are only able to connect to TwinCAT with one of the two ports. Additionally, it only works with disabled Fast Link Detection.

For our board, the PHYs are configured as follows:

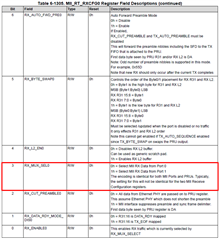

#define ECAT_PHYADDR_IN (1u)#define ECAT_PHYADDR_OUT (0u)#define ECAT_PHYPOLINVERT_IN (true)#define ECAT_PHYPOLINVERT_OUT (true)#define ECAT_PHYUSERXLINK_IN (false)#define ECAT_PHYUSERXLINK_OUT (false)A remark to the configuration: I had to swap the addresses of In and Out against my actual expectations of how they should be. Before the swap, I was not able to find the device on any of the ports. Additionally, the device is not found with ECAT_PHYUSERXLINK_IN/OUT (true). I also tried both PHYPOLINVERT settings. MDIO__REGS_LINK_REG is set to 1, as i connect the device, so it should be High active.

I also checked the PHY registers in the connected state. Apart from the PHY address, both are identical. The values are as in the following table:

| Port 1 connected | Port 2 connected | |

| BMCR_REG(00) | 0x3100 | 0x3100 |

| BMSR_REG(01) | 0x786d | 0x786d |

| PHYIDR1_REG(02) | 0x2000 | 0x2000 |

| PHYIDR2_REG(03) | 0xa240 | 0xa240 |

| ANAR_REG(04) | 0x01e1 | 0x01e1 |

| ANLPA_REG(05) | 0xcde1 | 0xcde1 |

| ANER_REG(06) | 0x000f | 0x000f |

| ANNPTR_REG(07) | 0x2001 | 0x2001 |

| ANLNPTR_REG(08) | 0x5006 | 0x5006 |

| CR1_REG(09) | 0x0000 | 0x0000 |

| CR2_REG(0a) | 0x0122 | 0x0122 |

| CR3_REG(0b) | 0x040c | 0x040c |

| REGCR_REG(0d) | 0x0000 | 0x0000 |

| ADDAR_REG(0e) | 0x0000 | 0x0000 |

| FLDS_REG(0f) | 0x0000 | 0x0000 |

| PHYSTS_REG(10) | 0x0015 | 0x0015 |

| PHYSCR_REG(11) | 0x0108 | 0x0108 |

| MISR1_REG(12) | 0x6400 | 0x6400 |

| MISR_REG(13) | 0x2800 | 0x2800 |

| FCSCR_REG(14) | 0x0000 | 0x0000 |

| RECR_REG(15) | 0x0000 | 0x0000 |

| MISR2_REG(13) | 0x0000 | 0x0000 |

| BISCR_REG(16) | 0x0100 | 0x0100 |

| RCSR_REG(17) | 0x0049 | 0x0049 |

| LEDCR_REG(18) | 0x0400 | 0x0400 |

| PHYCR_REG(19) | 0x8c20 | 0x8c21 |

| 10BTSCR_REG(1a) | 0x0000 | 0x0000 |

| BICSR1_REG(1b) | 0x007d | 0x007d |

| BICSR_REG(1c) | 0x05ee | 0x05ee |

| CDDR_REG(1e) | 0x0102 | 0x0102 |

| PHYRCR_REG(1f) | 0x0000 | 0x0000 |

I also checked the EtherCAT status registers at offset 0x30090000 (device is connected in both cases, but without communication to TwinCAT):

| Port 1 connected | Port 2 connected | |

| 0x0110 | 0x11 | 0x21 |

| 0x0111 | 0x56 | 0x5D |

| 0x0130 | 0x01 | 0x01 |

| 0x0131 | 0x00 | 0x00 |

| 0x0134 | 0x00 | 0x00 |

| 0x0300 | 0x00 | 0x00 |

| 0x0301 | 0x00 | 0x00 |

| 0x0302 | 0x00 | 0x00 |

| 0x0303 | 0x00 | 0x00 |

| 0x0304 | 0x00 | 0x00 |

| 0x0305 | 0x00 | 0x00 |

| 0x0306 | 0x00 | 0x00 |

| 0x0307 | 0x00 | 0x00 |

| 0x0308 | 0x00 | 0x00 |

| 0x0309 | 0x00 | 0x00 |

| 0x030A | 0x00 | 0x00 |

| 0x030B | 0x00 | 0x00 |

| 0x030C | 0xFF | 0x00 |

| 0x0310 | 0x00 | 0x02 |

| 0x0311 | 0x04 | 0x00 |

| 0x0312 | 0x00 | 0x00 |

| 0x0313 | 0x00 | 0x00 |

We have two questions:

1) Can you see a reason, why we cannot find our device on the second port?

2) Why ist the device not found, if fast link detection is enabled? This is a feature, which we want to support.

Please let me know if you need any further details. Thanks in advance for your support!

Best regards

Christian