Part Number: AM2432

Other Parts Discussed in Thread: AM6412, AM6422, AM6442, AM2434

Tool/software:

Hi,

My customer has a question about Application Note : “AM6442 , AM6422 , AM6412 and AM2434 Processor Schematic Design Guidelines and Schematic Review Checklist”.

The second half in the chapter 7.3.1.4 seems to be the same as the connection on AM64x/AM243x EVM.

On their custom board, the Ethernet PHY is reset only by the GPIO, without an AND gate. There is only turn the power on and off, No warm reset and No EPHY boot.

This is different from the recommendation in the Application Note below, are there any issue or risks ?

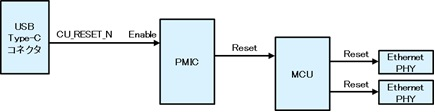

7.3.1.4 Ethernet PHY Reset

The recommendation is to implement the attached device reset using a 3-input ANDing logic. Processor general

purpose input/output (GPIO) is connected as one of the input to the AND gate with provision for pullup (to

support boot) near to the input and 0Ω to isolate the GPIO for testing or debug. The other two AND gate inputs

are the main domain POR (cold reset) status output (PORz_OUT) and main domain warm reset status output

(RESETSTATz) signals.

If a dual input AND gate is used, PORz_OUT or RESETSTATz can be connected as one of the input along with

the processor GPIO input as the second input based on the use case.

Thanks and regards,

Hideaki