Tool/software:

Hello TI Team,

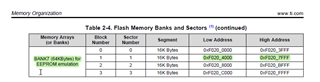

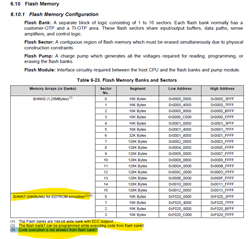

We are using the TMS570LS1227 microcontroller in our aerospace program. This device includes two flash banks, BANK0 and BANK7. According to the reference manual, BANK7 is intended for EEPROM emulation and does not support code execution from its flash memory.

Our plan is to program the "Dataload software," which is non-critical and does not need to execute during flight, into BANK7. During maintenance, the system will copy the Dataload software from BANK7 flash to RAM, swap the memory (flash and RAM), and reset the CPU to execute the Dataload software from RAM.

I have the following questions regarding this implementation:

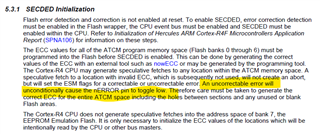

1. The Dataload software size is approximately 50 KB. Can we program the Dataload software into BANK7? Are there any differences in the programming process between BANK0 and BANK7 flash memory? Please note that we do not plan to use ECC for the Dataload software, whereas ECC will be used for the flight software. We will disable ECC before running the Dataload software.

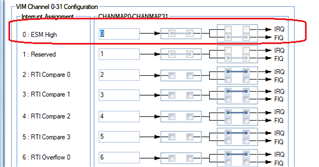

2. While running the flight software, if control unexpectedly jumps to BANK7 flash memory where the Dataload software is stored, will the processor trigger any NMI (e.g., will the ESM pin assert)?

I look forward to hearing from you. Thanks.

Best regards,

Jagadish