Tool/software:

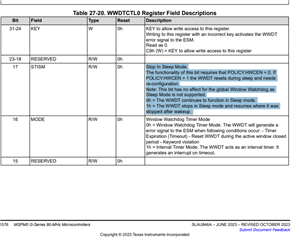

Page 1576 of the data sheet - "STISM - Stop In Sleep Mode. The functionality of this bit requires that POLICY.HWCEN = 0. If POLICY.HWCEN = 1 the WWDT resets during sleep and needs re-configuration. Note: This bit has no effect for the global Window Watchdog as Sleep Mode is not supported. 0h = The WWDT continues to function in Sleep mode. 1h = The WWDT stops in Sleep mode and resumes where it was stopped after wakeup."

Page 1576 of the data sheet makes reference to "POLICY.HWCEN" and "global Window Watchdog" which, when searched for in the data sheet and the entire internet, appear exactly nowhere else. Others may not share my view but the watchdog timer is like airbags in your car, or a parachute. Safety equipment that must be 100% bulletproof and always work. Which brings me to my point which is best I can tell its the most poorly documented peripheral and it should be the opposite, the most well documented peripheral. I was getting unpredictable and erratic behaviour with the WWDT0 sometimes running and sometimes not while in sleep mode. And yes, STISM bit is set to true. One other flaw of WWDT design is its impossible to verify the counter is really counting. There are status bits like the "RUN" bit that allege its running but from my testing it is NOT running but again, since you cant view the actual counter register there is no way of knowing other than to wait for your WWDT0 event to _not_ happen when it should. Very frustrating. I instead implemented my own watchdog using timerg0 which always runs in standby/low power.