Tool/software:

Hi,

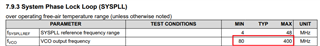

I want to use the internal oscillator to generate a 80 MHz clock. I have used to following configuration :

2 questions :

- Is it the recommended way to clock the MCU at 80 MHz without using an external oscillator?

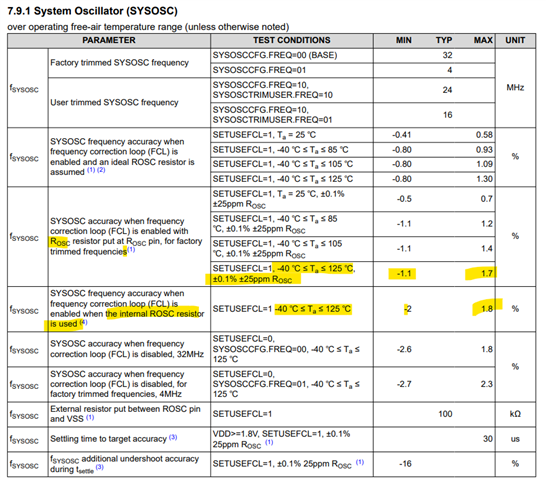

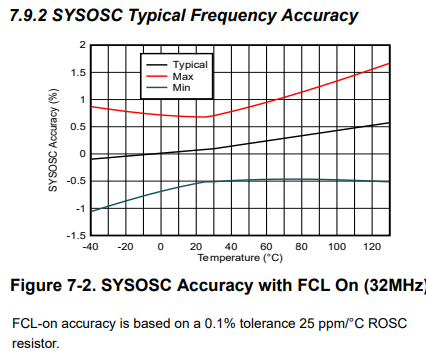

- Is the accuracy (7.9.1.1 SYSOSC Typical Frequency Accuracy from the datasheet) impacted going through the PLL ?

Thanks,

Geoffrey