Tool/software:

Hi,

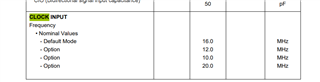

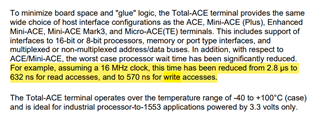

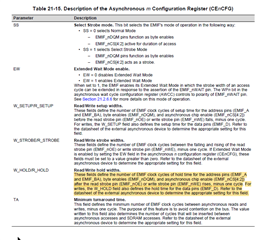

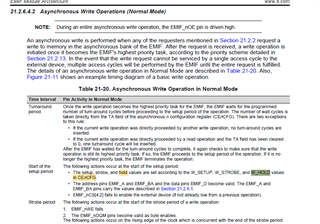

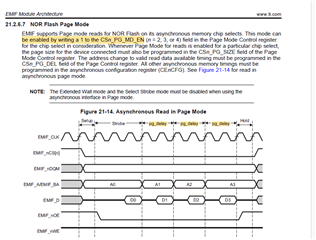

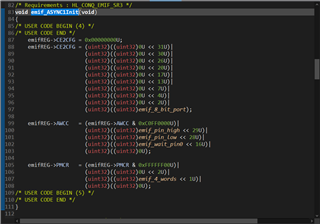

I am currently facing an issue with EMIF during write operations. My objective is to achieve the maximum speed of EMIF, and for that, I have configured the lowest possible timings in the Asynchronous Configuration Register (CE2CFG). Specifically, I have set the write and read setup, strobe, and hold times to 0.

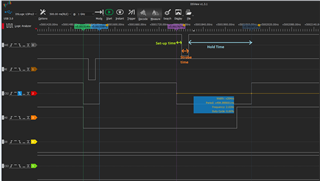

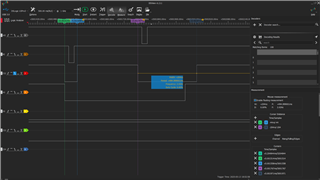

Based on this configuration, the expected time to write one byte of data to external asynchronous memory should be approximately 40 ns for both read and write operations. However, in practice, I am observing that the write operation takes around 220 ns, which is significantly higher than the configured value. On the other hand, the read timing is close to the expected value at approximately 44 ns.

I have attached the logic analyzer capture and the EMIF configuration screenshot for your reference.

Could you please help me identify the cause of this discrepancy and suggest possible solutions to achieve the desired write performance?

Thanks,

Regards,

Veerappan P.