Tool/software:

Hi TI experts,

We are having issue with Omron PLC for AM2432 drives, while XMC4800 drives are OK.

The simplified connection is,

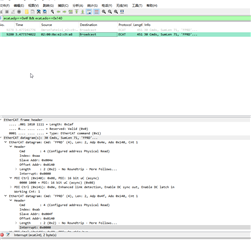

Omron NX701 - network analyzer - XMC4800 (adp 2) - AM2432(adp 1)

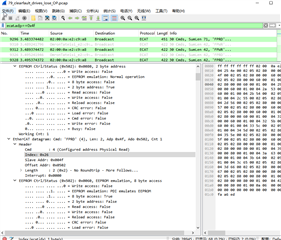

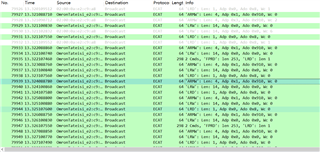

1. With First power up / PLC program download, drives becomes OP correctly.

2. When clearing fault is issued, nothing happens

3. XMC4800 is power off, power up, clear fault from PLC to set all drives back to OP.

4. When more Clearing fault command is issued, nothing happens.

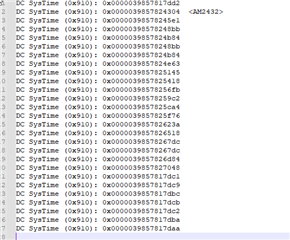

5. AM2432 is power off (drive_power_off.pcap), power on, clear fault to set all drives to OP(drive_power_on_reset_to_op.pcap)

6. When 2nd clear fault command is issued, AM2432 is set back to Init (After_power_on_reset_to_Init.pcap).

7. When 3rd Clear fault command is issued, AM2432 is set to OP (After_power_on_Init_reset_to_OP.pcap)

8. step 6 & 7 can be repeated to reproduce the issue.

9. If cable between AM2432 and XMC4800 is disconnected & connected, repeat step 6 & 7 would no longer reproduce the issue.

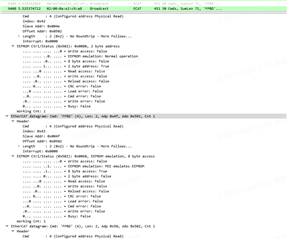

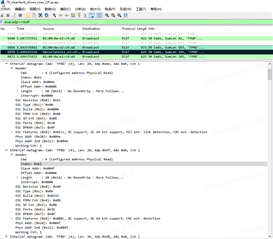

So I think the connection behavior of AM2432 is different from power off & power on to cable disconnect & reconnect.

Code of AM2432 is reduced to beckhoff slave stack built from SDK and the issue persists.

One noteable issue is that when powering of AM2432, the package is lost for 150 ms.

So we think PHY might still be active while PRU is not active.

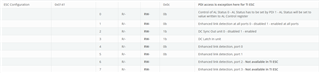

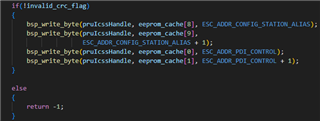

Now phy is reset when AC loss fault is detected(this would not fix the Omron issue).

PHY reset is also applied on first time Init to PreOP( which could fix the issue).

However we are thinking if the reset can be put on power up (tested but not working), and if anyone can understand the fundamental difference that caused the issue

Thanks.