Part Number: AM263P4

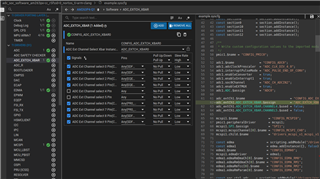

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

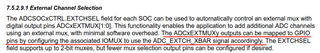

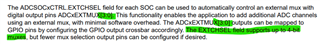

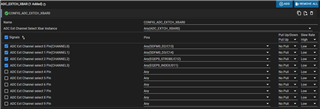

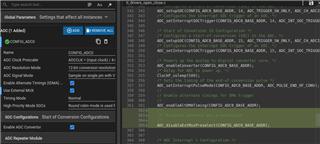

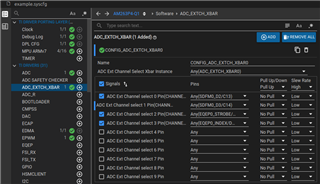

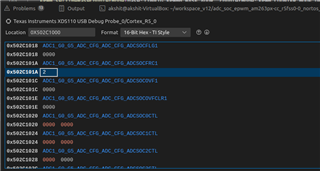

I am attempting to use the External Mux functionality of ADC0 through SysConfig. However, it appears that the "Use External Mux" checkbox is the only option available regarding this functionality. The Technical Manual gives rough details of how to make use of the external mux, but of course does so with no references to what SysConfig will/won't be doing as part of the setup and execution. It also appears that there are no examples in the SDK that use this functionality. I am looking for guidance on how to properly configure the ADC in SysConfig, and that what additional API commands need to be placed in code for setup and execution.