Tool/software:

In AM26P4 ADC maximum conversion time is mentioned as 250ns in datasheet.

Is it the time for sample&hold (ts+h) +Conversion(t EOC)?

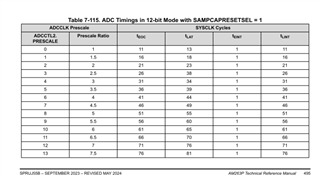

If yes then according to the table 7-115 mentioned in manual , ADC requires 76 System Clock cycles (76*5ns = 380ns) for t EOC alone which is greater than max conversion time 250ns.

Could you please explain how to set ADC for 4msps, 3msps, 2msps.