Part Number: MSPM0G3519

Tool/software:

Hello colleagues, i have a question concerning behavior of the SPI controller in controller mode, particularly setting

DL_SPI_FRAME_FORMAT which has options:

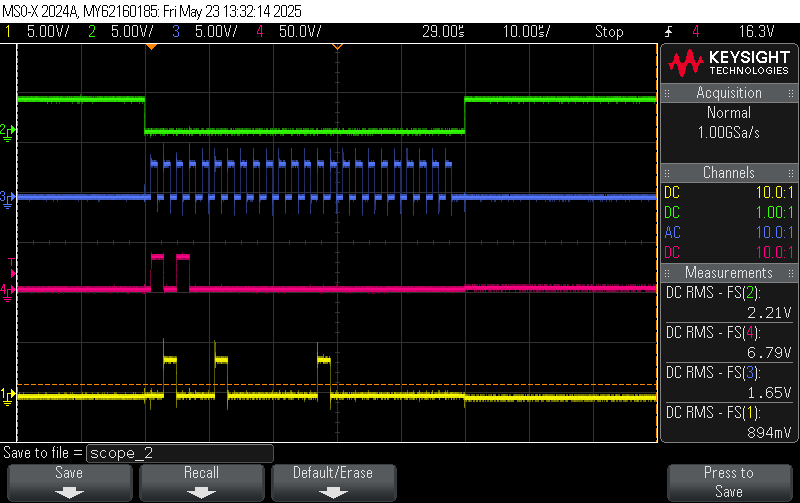

(in both cases FIFO has 3 bytes of data 0xA00000 - and it is clearly seen on the OUT of the waveform)

if the option DL_SPI_FRAME_FORMAT_MOTO4_POL0_PHA1 is selected the following controller behavior is observed (green - CS, blue - SCLK, purple - OUT)

but if