Tool/software:

Hi,

MSPM0 promotion slides say MSPM0 devices are pin-2-pin compatible if package is the same.

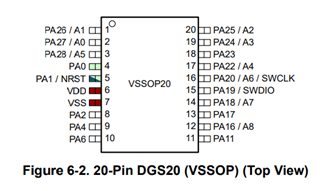

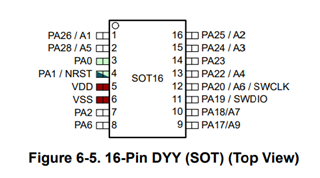

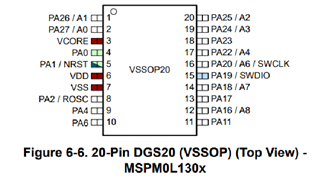

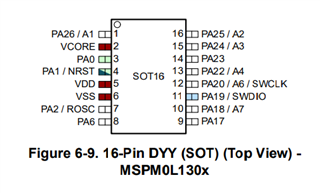

My customer is interested in C110x and L130x devices. Target packages are DGS20(VSSOP20) and DYY(SOT16).

According to each data sheet, there are a few differences in pin diagram and pin handling requirements.

C110x Datasheet:

L130x Datasheet:

Main differences are:

- L130x has vcore pin and it must be connected to Cvcore capacitor.

- L130x has ROSC pin and Rosc resister is connected on board.

Questions:

Q1) These pins need to handled differently for C110x and L130x?

(not pin-2-pin compatible in fact?)

Q2) Any other pins need to handled separately?

Thanks and regards,

Koichiro Tashiro