Other Parts Discussed in Thread: TMS570LC4357

Tool/software:

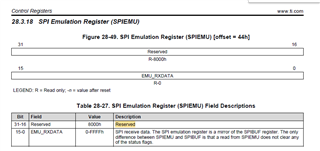

With reference to SPNU515C

The field description for SPI Emulation Register (SPIEMU) states the following:

Value 8000h

Description Reads return 0. Writes have no effect.

1. The value and description contradict one another.

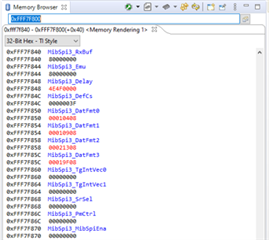

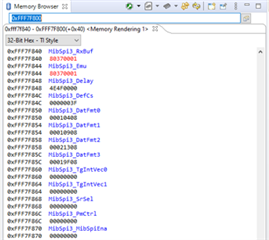

2. The value that I am actually seeing when reading the upper 16 bits is 8037h

What is the expected value when reading bits 31-16 of the SPI Emulation Register (SPIEMU)?