Part Number: MSPM0G3507

Tool/software:

Hello,

My customer is developing with MSPM0G3507.

And they have question about TIMx event delay time.

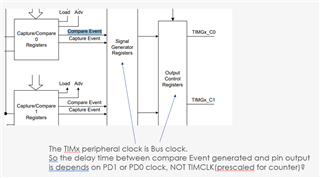

Question1

If the PWM output using "Output control Registers", The delay time of between Compare Event and Pin Output(Hi ->Low) depends on which (TIMCLK or peripheral bus clock) clock?

In their test, the delay time is related TIMCLK. (if TIMCLK use more fast clock (change prescale value), the delay time was more less.)

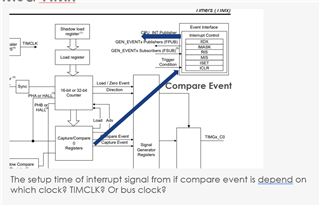

Question2

If GPIO output use compare interrupt, The delay time between Compare event and Pin output depends on periperal bus(PD0 or PD1) and CPUCLK?

I believe this delay time is const, even if change TIMCLK prescaler. Is this correct?

Thanks,

GR