Tool/software:

Hi,

Could you kindly review my timing analysis?

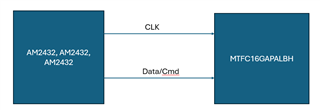

We are planning to use the below devices in the upcoming project.

SoC:

Legacy SDR mode:

Tclk(MMC0) = 40ns

Td= Tclk-dV or Tclk-cmd = min(-2.3ns), max(2.9ns)

eMMC : JEDEC Complaint

Tsetup(min) = 3ns

Thold(min) = 3ns

Toutput_delay(min/max)= 2.5ns/13.7ns

Let’s say SoC is driving the clk and command, in that case below will be our timing analysis

Td + Tpcb_data_delay(max) < Tpcb_clk_delay + Tclk - Tsetup_emmc ---------------- eq1

Tpcb_data_delay(max) - Tpcb_clk_delay < Tclk - Tsetup_emmc – Td

Tpcb_data_delay(max) - Tpcb_clk_delay < 40- 3-2.9

Tpcb_data_delay(max) - Tpcb_clk_delay < 34.1ns

Td + Tpcb_data_delay(min) > Thold_emmc + Tpcb_clk_delay -------------------------eQ2

Tpcb_data_delay(min) - Tpcb_clk_delay > Thold_emmc - Td

Tpcb_data_delay(min) - Tpcb_clk_delay > 3-(-2.3)

Tpcb_data_delay(min) - Tpcb_clk_delay > 5.3ns

That means my data or command trace delay should fall between 5.3 ns and 34.1 ns relative to the clock.

Assuming a standard PCB trace delay of 150 ps/inch, achieving a 5.3 ns delay would require routing the trace approximately 35 inches longer than the clock trace — which is clearly impractical.

I feel like I might be missing something here. Could you please help clarify?

Is there any eMMC routing guidelines available with the skew details in any of the TI documentation?