Part Number: TMDSEMU110-U

Tool/software:

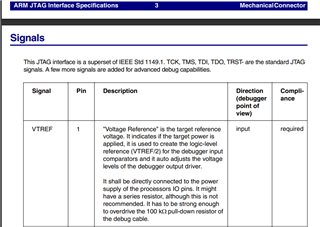

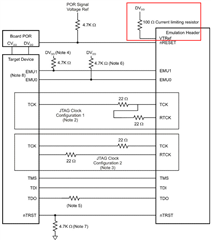

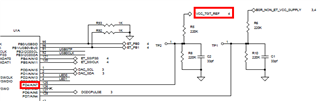

For the CTI-20 pinout, pin 5 VTRef. I found some internal documentation at the company I work for that calls out there is a 100Ω+diode pull down on this pin internal to the device. I can't find any information in the user manual or app note that calls this circuitry out. Wanted to confirm what the internal circuitry for this pin looks like and if there is no pull-down circuit, what is the expected current draw on this pin?

Thank you for your time.