Part Number: AM2634

Other Parts Discussed in Thread: TMDSCNCD263, AMC1306EVM

Tool/software:

Hi all!

I am trying to run the SDFM EPWM sync CPU read example on my tmdscncd263 control card.

Running CCS Version 20.1.1 (20.1.1.466), MCU SDK - mcu_plus_sdk_am263x_10_01_00_31. I am running the imported project without modification.

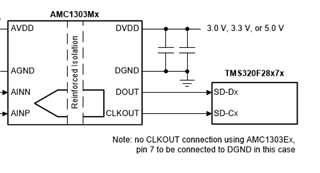

I have a single AMC1306EVM I am powering and sourcing to D0. I have confirmed this IC is working as I can see DOUT output a digital signature when using the PWM waveform as a clk source (see below).

I have 3 problems on this project:

- Where I am seeing DebugP_log messages in CIO from other imported projects, I am not seeing them from running this project.

- I can see some DebugP_log when running `screen` locally, but i never see the startup messages

- DebugP_log("SDFM EPWM Sync CPU Read Test Started ...\r\n");

DebugP_log("Please wait %d seconds ...\r\n", APP_RUN_TIME);

- DebugP_log("SDFM EPWM Sync CPU Read Test Started ...\r\n");

- I do see the following from `screen

- SDFM ISR count: 0

Modulator failure - (repeat)

- SDFM ISR count: 0

- I can see some DebugP_log when running `screen` locally, but i never see the startup messages

- When attaching a scope to HSEC Pin 72 (SDFM0_CLK0), I don't see any waveform.

- It does not seem like the clock is correctly enabled in the example code.

- I do need the output clk working, I cannot rely on a PWM output as the clk source.

- If I plug the ePWM HSEC Pin 51 output into my SDFM AMC1306EVM as the clock source, I do see the SDFM IC output a digital signature on DOUT.

- But the Sitara does not seem to receive the D0 data result or process it.

- The sdfmISR1 function does not seem to ever trigger (confirmed by using a breakpoint during debugging).

- Is this a result of the int_xbar not configured?

And a quick observation

- The clock sources for SDFM_FILTER_2, 3, 4 are configured but it does not look like 1 is. Is this done on purpose? If so why?

- Note, I have added a line configuring SDFM_FILTER_1 and it does not solve my issues above.

- github.com/.../sdfm_epwm_sync_cpuread.c

Any help is appreciated! This topic is required ASAP for my use case. If some expert wouldn't mind reviewing or rerunning the example code that would be incredible.

Thank you kindly!