Other Parts Discussed in Thread: DP83640

Tool/software:

Hi all,

I’m investigating the interaction between the TMS570LC4357’s EMAC and a DP83640 PHY over an MII connection.

What I observe:

When there is no Ethernet link (e.g., unplugged cable, link down), the MII bus is still active (i.e., clocks are available), and the EMAC processes the TX buffers as normal—the EOQ (End Of Queue) flag is correctly handled.

However, when the MII clock itself is absent (e.g., if the PHY is held in reset or not providing MII clocks), the EMAC does not process TX buffers and the EOQ flag in the descriptor chain is never reached.It looks like the TX state machine does not step at all in this condition.

My current hypothesis:

The EMAC’s internal synchronization logic or state machine requires the MII clock to advance, and when the clock is missing, the EMAC simply stalls. Unfortunately, I can’t find any block diagram or detailed information in the documentation that explicitly explains this behavior.

My questions:

Is it expected that the TMS570 EMAC will process TX descriptors regardless of link status, as long as the MII clock is present?

Does anyone have documentation, block diagrams, or internal state diagrams that clarify why the EMAC TX path stalls only when the MII clock itself is missing, and not simply based on link status?

The main Question is ;

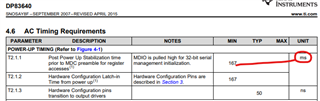

Other than simply waiting a little bit , Is there a recommended way (through status registers, hardware mechanisms, or proven techniques) on the TMS570LC4357 or DP83640 to directly detect the presence of the MII clocks from the PHY before initiating any EMAC transfers? It appears that the DP83640’s MDIO interface and responses become available even before the MII clock outputs are fully stabilized.

my init call flow is like this

-reset emac

-init emac control

-init emac ( but not enable mii yet)

-init mdio

-init dp83640

-init emac buffers etc.

-enable mii

Thank you!