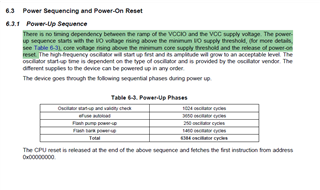

Part Number: TMS570LC4357-SEP

Other Parts Discussed in Thread: LAUNCHXL2-570LC43, TL7700-SEP, SN54SC4T08-SEP, TPS7H4010-SEP

Tool/software:

Hello,

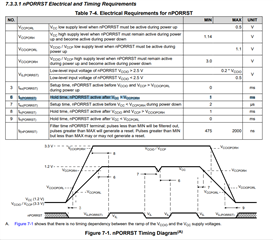

I need some clarification regarding the operation of the nPORRST pin on the MCU.

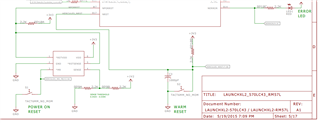

In the LAUNCHXL2-570LC43 LaunchPad schematic, only the 1.2V core voltage is monitored using a voltage supervisor. There's no supervisor for the 3.3V IO supply. This raises a concern because if the 3.3V rail drops below its minimum operating voltage, it could cause unpredictable behavior on the IOs.

In contrast, the TMS570LC43x HDK EVK schematic includes voltage supervisors for both 1.2V and 3.3V.

Questions:

-

Which approach is recommended — monitoring only 1.2V or both 1.2V and 3.3V?

-

In my design the power sequencing is:

1.2V (Vcore)→3.3V (Vccio). -

Currently, I've pulled up the nPORRST pin to 3.3V using a 10k resistor. However, based on TI forum posts, it seems this approach is not recommended.

Proposed Solutions:

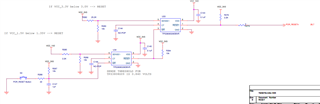

I'm considering using two TL7700-SEP voltage supervisors (one for 1.2V and one for 3.3V, their Tpo set to 1.1ms) and feeding their outputs into an AND gate (SN54SC4T08-SEP). The AND gate output would drive the MCU's nPORRST pin.

-

Is this a valid and reliable approach?

Alternatively, I'm using the TPS7H4010-SEP buck converter to generate 1.2V and 3.3V. The PGOOD output of 1.2V buck drives the EN pin of the 3.3V converter. I could also connect both PGOOD signals to the inputs of the AND gate and drive nPORRST from its output.

However, in this configuration, I'm concerned about meeting the minimum 1 ms nPORRST hold time requirement, as PGOOD signals might deassert too quickly.

Request:

Please advise:

-

Which approach is more suitable?

-

Is there a simpler or more reliable alternative to manage the nPORRST signal correctly?