Tool/software:

Hello,

We seem to be experiencing an MPU/Firewall related issue for a device recently converted to HS-SE, where this is not seen on a HS-FS device.

Setup is baremetal, cores 0+1 in lockstep, cores 2+3 standalone.

Just after switch from bootloader into Application, when accessed from core0, all of our OCRAM banks (0-5) seem to be initialised as RAM adress 0x702FFFFF is visible from core0:

However, when looking at the same memory space from core 2, this memory space shows up as uninitialised:

instead, we can see memory space up to 0x701FFFFF or thereabouts) being initialised:

The same is the case for core3.

This implies that for R5SS0 OCRAM banks 0-5 are initialised OK, but for R5SS1 only OCRAM banks 0-3 are initialised OK.

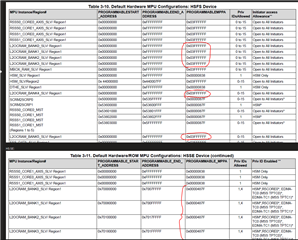

Looking at the TRM, the default MPPA regions for MPU regions does differ between HSFS and HSSE modes - but we do have priviledged access for R5CORE0 for all OCRAM banks.

But currently doing some more decoding where this could be coming from. We're only initialising OCRAM from core0 instead of through the HSM, maybe that's a mistake?

Will read out and try decode MPPA_X regions for MPU regions setting bank4 and bank5 permissions.

We currently don't specify firewalls in the SBL directly, maybe something needs to be configured there to allow initialisation of R5SS1 through R5SS0.

Does anyone have any pointers how to debug this further? We don't see this behaviour for HSFS devices, but the only relevant variation from HSFS to HSSE I can find is that section mentioned above in the TRM on this topic.

Thanks,

Rens