Other Parts Discussed in Thread: DP83TG720-EVM-AM2, SYSCONFIG

Tool/software:

Hi!

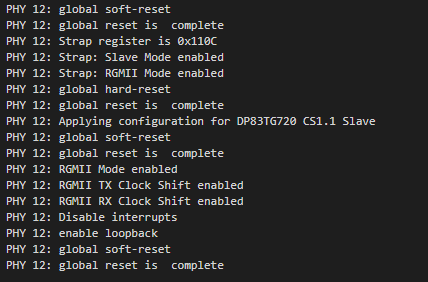

I am trying to enable Automotive Ethernet add-on Board (DP83TG720-EVM-AM2) on AM263px Control Card (TMDSCNCD263P PROC159A).

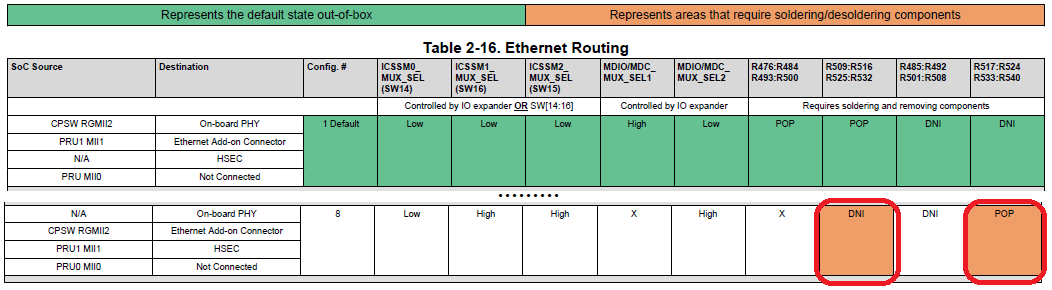

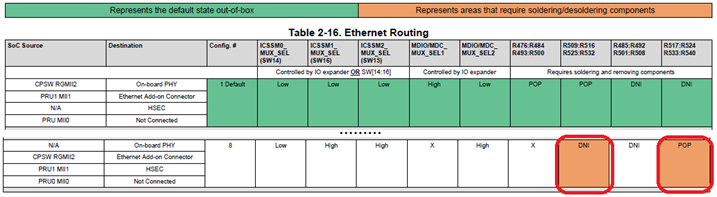

I re-soldered zero-ohm resistors on the control card according to Config. #8 in Table 2-16 from the control card User Guide.

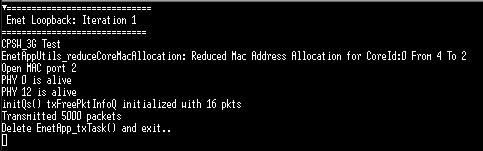

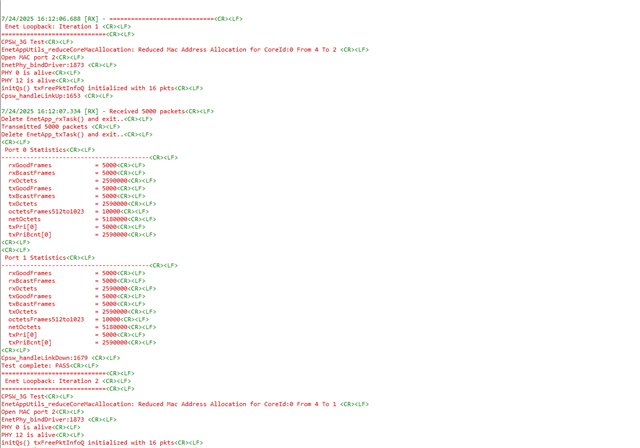

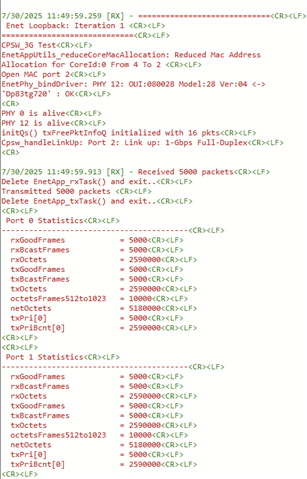

I am trying PHY loopback test from Enet CPSW Loopback Example.

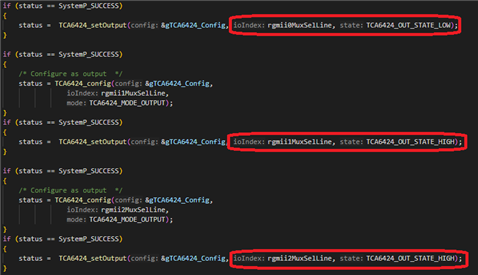

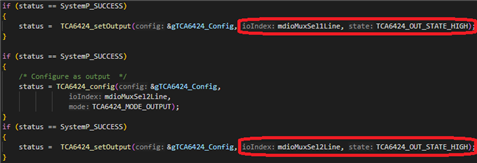

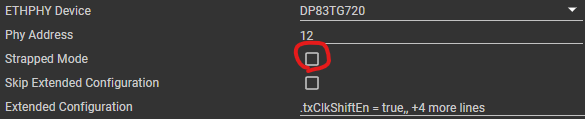

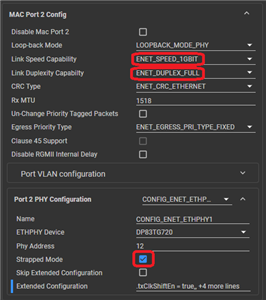

I made changes in the Sysconfig file from the example as described here.

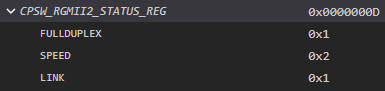

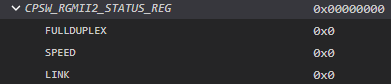

As a result, the transmission fails.

While checking the signals on the add-on PHY board, I observe 25 MHz on Tx clock pin.

As I understood from PHY documentation, this clock is provided by MAC, and it should be 125 MHz. Therefore, it looks like the problem is on MAC side.

I would be thankful for any suggestions for further debugging or proper configuration.