Part Number: AM2432

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi experts,

I am working on the Sigma-Delta (SDFM) examples with Motor Control SDK 09.02.00.11 looking at the Fast Detect and having some questions:

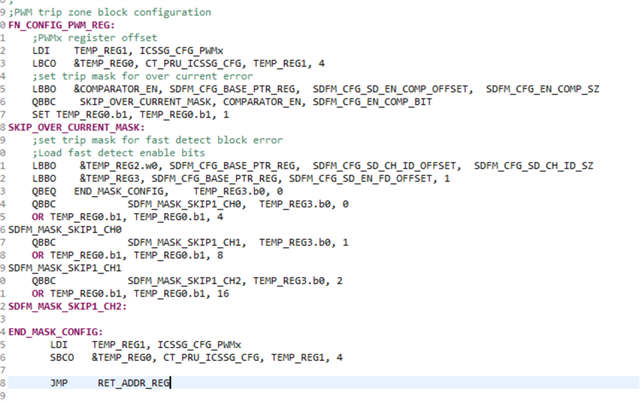

1) The PRU ICSS PWM TZ_OUT signal (for Fast Detect) is an active-high signal. What do I need to change at the SDFM firmware to invert the polarity of the PRU ICSS PWM TZ_OUT signal?

2) It seems that the Fast Detect only works if the Fast Detect option is enabled for CH0. If I disable the Fast Detect for CH0, it no longer works for the other channels. Why is that, and what do I need to change to make it work?

3) When will the new Motor Control SDK be released?

Thanks!

Best regards,

Jan