Part Number: TMS570LS1224

Tool/software:

Hi,

We been successfully using a TMS570LS1224 device for many years in our products. To date we have used the SPI ports in 8 or 16 bit mode.

We now have a requirement to generate a 32-bit continuous serial data word, however the device only supports 16 bits per word.

We have tried setting the device onto 16-bit mode and loading two 16-bit words back-to-back (ie not waiting for TX to complete before loading the next word).

We can get the 32 bits out of the device at the required rate (2MHz), but there is a small delay inserted between the first and second 16-bit word (approx. 60ns).

This is causing us an issue with our receiving device as the inserted gap is causing data corruption.

is there any way to reduce this gap / reload time. I assume this is an internal SPI hardware fetch time, when loading the next data word from the buffer?

We currently have the device configured as follows:-

SPI Channel = SPI3

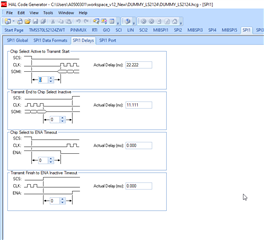

Write Delay = 0;

Parity Polarity = EVEN (0);

Parity Enable = ENABLE (0);

Wait On Enable = NO_WAIT (0)

Shift Direction = MSB_FIRST (0);

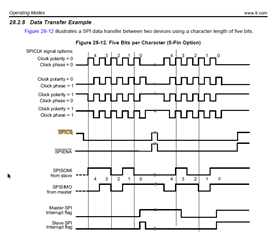

Clock Polarity = POLARITY_LO (0);

Clock Phase = NO_DELAY (0);

Bit Rate = 2MHZ;

Data Word Length = 16U;

We can resolve this using external shift registers, but had hoped to utilise the internal SPI for this if possible as we are very short on real estate on our board.

Any advice you can provide would be greatly appreciated.

Kind regards,

Paul