Tool/software:

Hi:

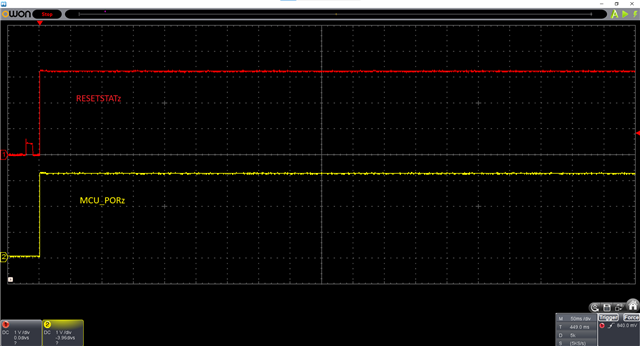

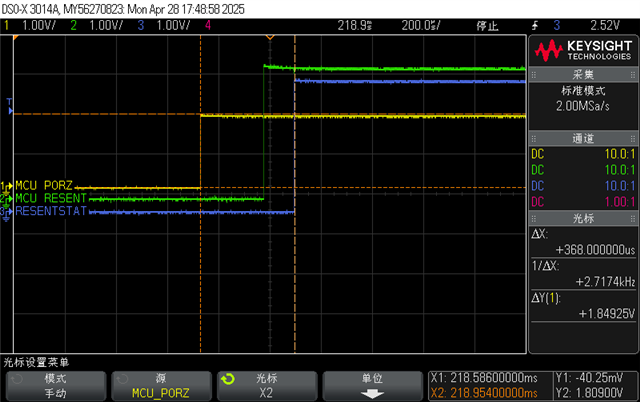

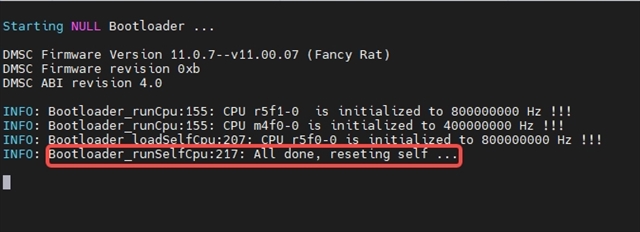

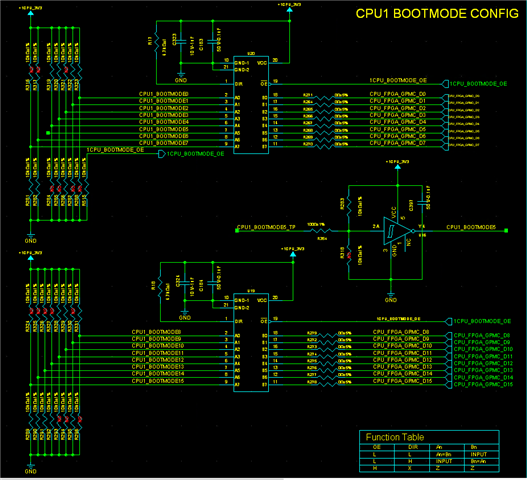

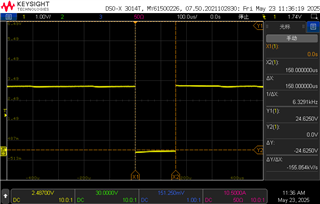

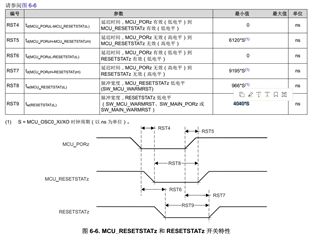

We found in our testing that after the AM2432 MCU-PORz signal is released, the RESETSTATz and MCU-REETSTATz will be pulled low, but the RESETSTATz low level time tW (158us)is less than the 4040 * S (161.6us)required in the datasheet.What's the solution to this problem? What are the implications?

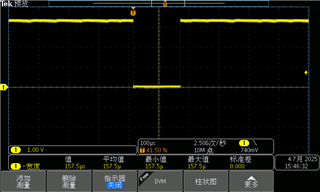

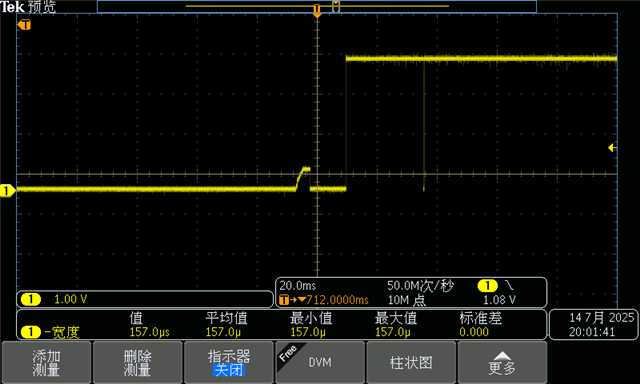

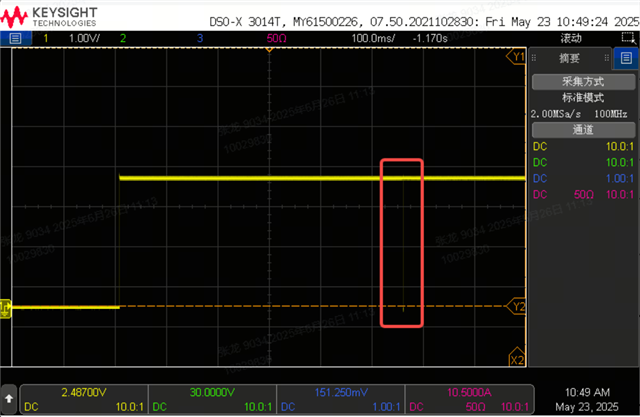

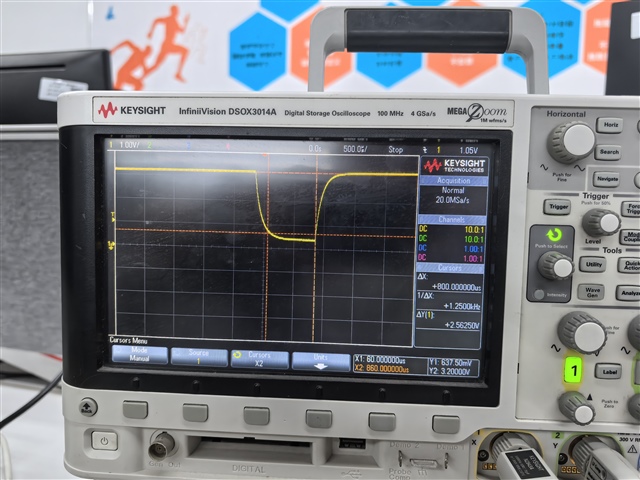

Figure 1 the RESETSTATz singal POWER UP

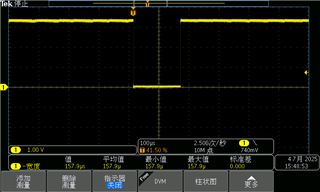

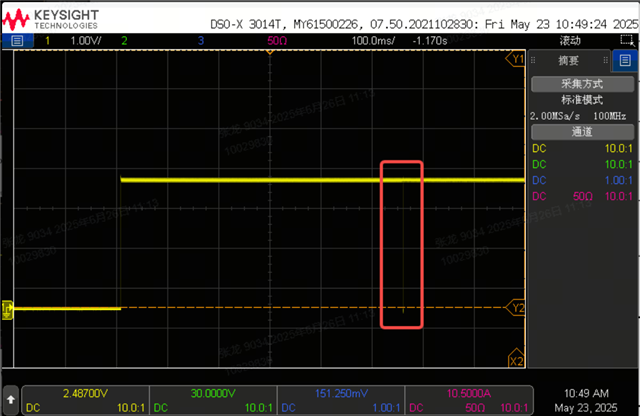

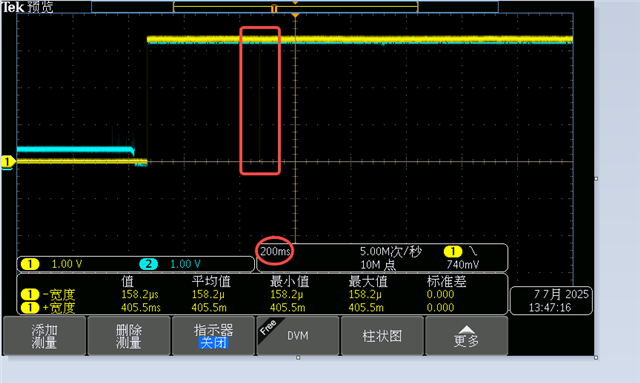

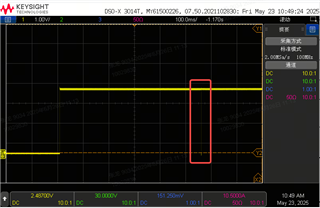

Figure 2 we test RESETSTATz POWER UP (zoom enlarge)

Figure 3 AM2432 datasheet specifications