Tool/software:

Hi:

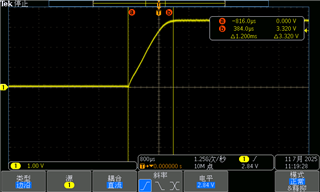

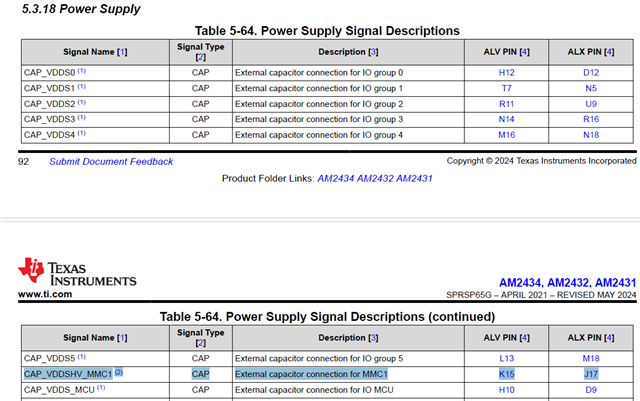

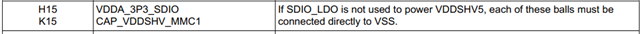

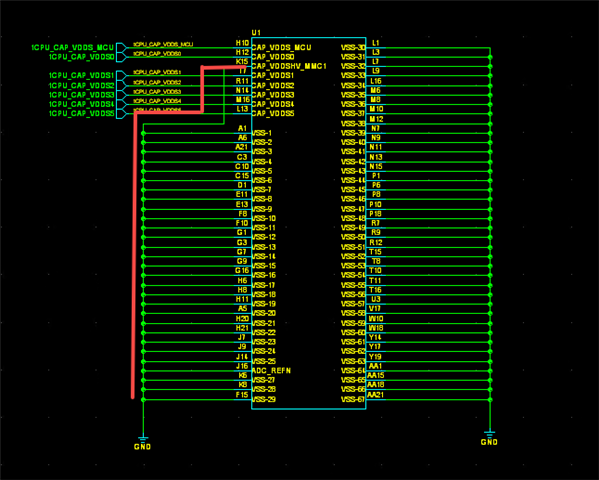

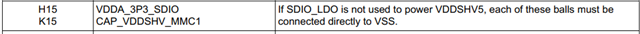

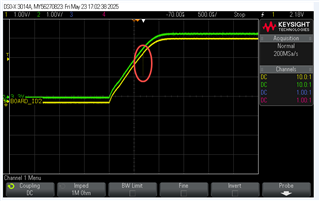

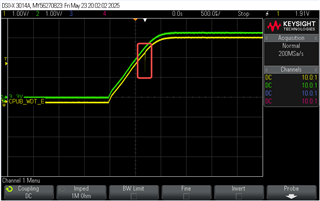

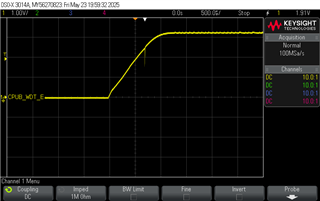

We found in our testing that multiple GPIO external 10K resistors of AM2432 were pulled up to VCCIO, which was 3.3V. However, during the power on process, the GPIO pin level was not monotonic. We synchronously tested the GPIO level and the VCCIO level when powered on together, as shown in Figures 1 and 2. The VCCIO level was monotonic, so this problem is not caused by the power supply. I have consulted a lot of information, and my conclusion is that many GPIO of AM2432 are in a floating state during the reset period and after reset release (but before software initialization), which makes the parasitic capacitance of the pins easy to cause interference during power on. Is my understanding correct? We hope TI can provide me with a more authoritative and credible explanation regarding this issue. Thank you!

Figure 1 and 2 GPIO Y7 test power up

Figure 3 and 4 GPIO V7 test power up