Tool/software:

Hi,

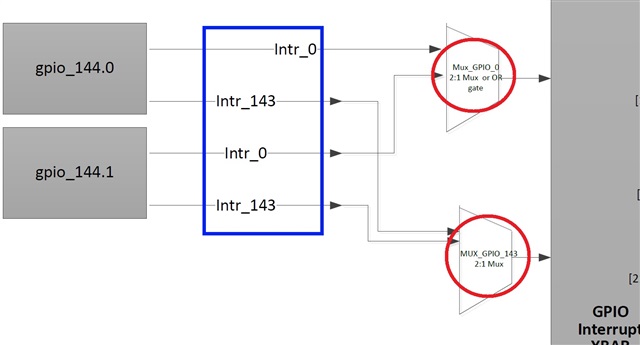

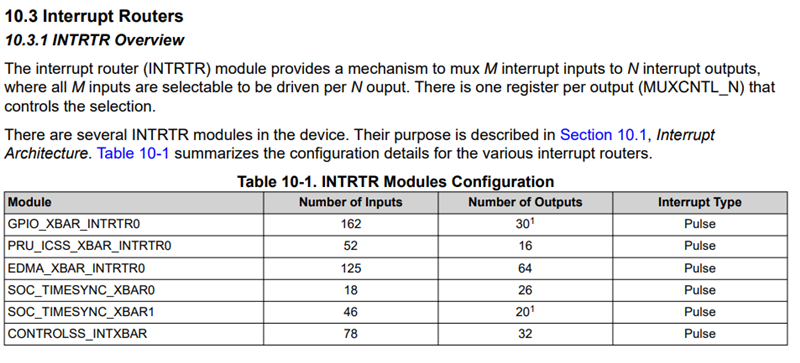

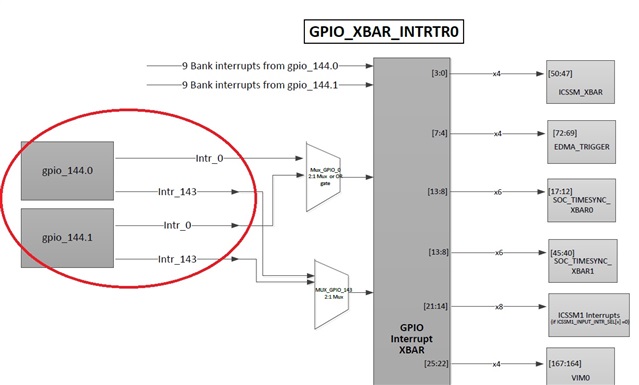

My customer has some questions about "Figure 4-33. GPIO XBAR Interrupt Router Integration Diagram" in the TRM. Could you help to answer their questions below ?

What does “0” of gpio_144.0 mean ? What does “1” of gpio_144.1 mean ?

The only intr_0 and intr_143 are output from gpio_144.0 or gpio_144_1.

They don’t understand this.

Could you explain this ?

Is there any document which explain this in detail ?

Thanks and regards,

Hideaki