Tool/software:

Hi team,

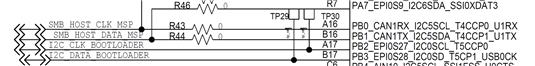

Customer is using MSP432E411YTZAD on their board with an I2C connection between the MCU and their Back End board (host of I2C/SMB). The I2C bootloader signals are connected to PB2/PB3 pins as shown in Table1 of BSL User's Guide and in their source code, the definition of PB2 and PB3 are default. They would like to do FW updates using these I2C signals (without using JTAG/J-Link) but aren't sure how to boot the BSL.

Given this, could you advise on the process to enable I2C bootloader function? I have requested they share their schematic and source code to check what they've implemented so far.

Best,

Luke