Part Number: AM2432

Tool/software:

Hi,

I am using AM2432 with the Industrial SDK 11.00.00.08.

I want to use the SA2UL subsystem to calculate SHA256 HMAC in my multicore project.

I looked at the crypto_hmac_sha256 example project. My project requires the calculation to be done by core R5FSS1-0, but the example is for core R5FSS0-0.

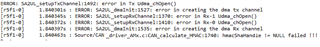

I saw that the first part of opening firewall has to be done by core R5FSS0-0 (as written here), so I moved that part to core R5FSS0-0 (with FreeRTOS) and I made sure that it is done before accessing the SA2UL subsystem. Then I moved the part of using the SA2UL subsystem in core R5FSS1-0 (in bare-metal), but now when I execute hmacShaHandle = Crypto_open(&gCryptoHmacSha256Context); I get SystemP_FAILURE in status = SA2UL_open(0,&prms); and I get these errors:

What am I doing wrong? Can the SA2UL subsystem also be used by core R5FSS1-0? Instead if I keep everything in the core R5FSS0-0 I have no problem at all.

Thank you,

Kind Regards,

Andrea