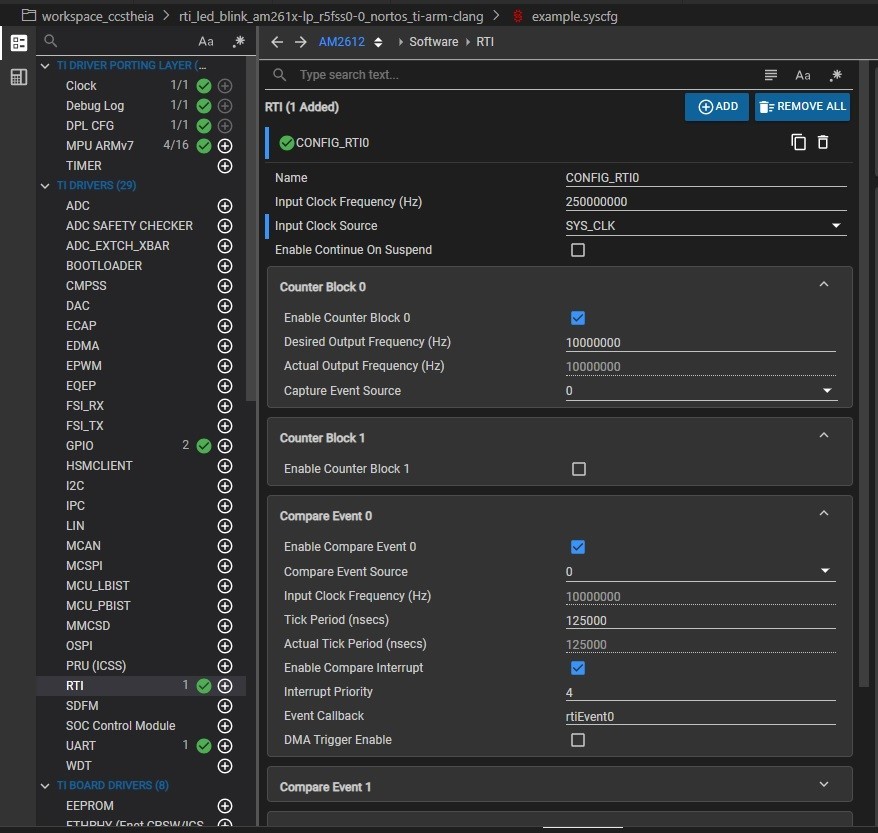

Part Number: AM2612

Other Parts Discussed in Thread: LP-AM261, SYSCONFIG

Tool/software:

Hi,

The customer is now evaluating AM2612 by using LP-AM261.

They’re considering to connect 25MHz crystal oscillator to EXT_REFCLK0.

This pin of EXT_REFCLK0 can be input up to 100MHz. Correct ?

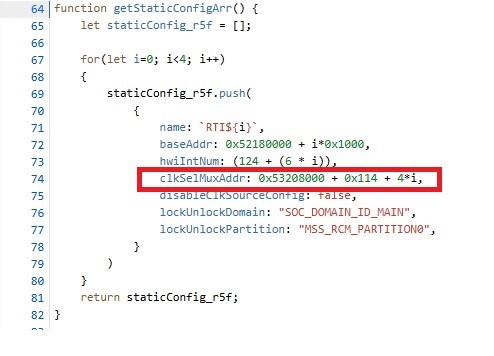

They’re evaluating the timer interrupt with the following configuration, and observing the period of timer interrupt by using the oscilloscope. It’ll be 125us period of timer interrupt.

When AM2612 is booted up with DEVBOOT mode, they can observe 125us period of timer interrupt as they expected.

However, it’ll be 1,250us when it is booted up with OSPI BOOT mode. It is 1,000 times longer period than they expected.

Do you have any solution to solve this issue ?

Thanks and regards,

Hideaki