Part Number: TMDS243EVM

Other Parts Discussed in Thread: TMDS64EVM

Tool/software:

Hi, experts.

I have two TMDS243EVM and am running PCIe example code.

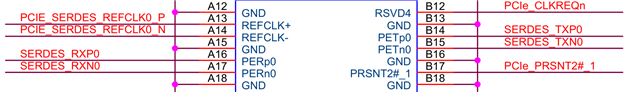

I connected the PCIe cable in the picture below to the PCIe connectors of the two boards

and downloaded pcie_benchmark_ep and pcie_benchmark_rc respectively and ran it,

but RC didn't respond(output).

Best Regards,