Other Parts Discussed in Thread: AM6442, SYSCONFIG

Tool/software:

Hi Team

We are currently trying to establish CAN-FD communication between an AM6442 and an F28P65x device. As per the CAN protocol, both ends must be configured with matching Nominal and Data Bit Timing parameters to ensure reliable communication.

On the AM6442 side, using TI’s SysConfig tool,we can clearly view the following:

-

Effective Nominal Bitrate: 1000 kbps (1 Mbps)

-

Effective Data Bitrate: 5000 kbps (5 Mbps)

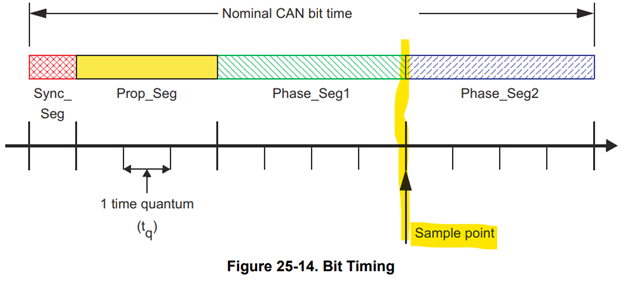

However, on the F28P65x side, the SysConfig file does not directly show the Effective Bitrates. Instead, we only have access to low-level timing parameters like BRP, TSEG1, TSEG2, and SJW.

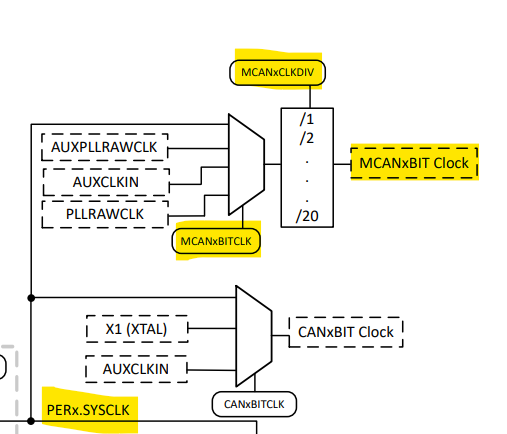

We are currently not sure what CAN clock frequency is being used internally for the CAN module on the F28P65x.

We have the following urgent questions:

-

What is the CAN module clock frequency on the F28P65x?

-

How do we configure the Nominal and Data bit timing parameters on the F28P65x side to achieve:

-

Nominal Bitrate: 1000 kbps

-

Data Bitrate: 5000 kbps

to match the AM6442 settings?

-

Additionally, we have already tried configuring the F28P65x with the standard bitrates used in the example projects, such as:

-

Nominal Bitrate: 500 kbps

-

Data Bitrate: 1000 kbps

But even those combinations are not working for us in establishing successful CAN-FD communication between the two devices.

If there are any tools, calculators, or guidelines recommended to compute the correct timing values based on the CAN clock, that would also be very helpful.

This is quite urgent for our project, and any support or guidance you can provide would be sincerely appreciated.