Part Number: MSPM0G3507

Tool/software:

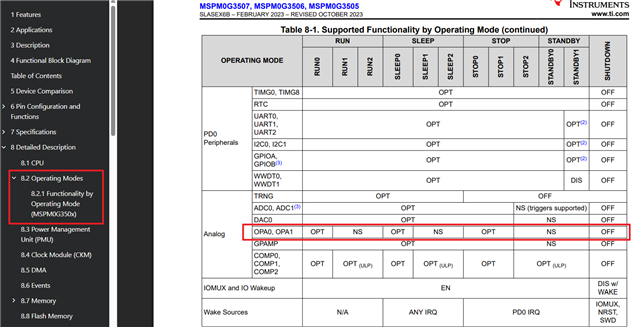

I'm working with a customer where we previously confirmed that the OPA can run in RRI mode with a 4MHz clock if the input is not changing (DC input). There was no slew rate check as part of the confirmation since the input is expected to be stable, not changing.

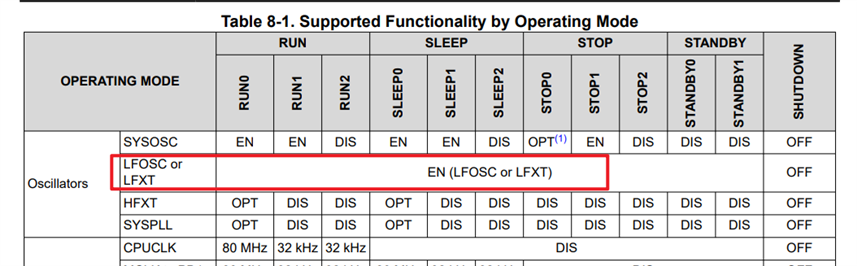

As a follow-up, the same customer is wondering if it is possible to use the OPA with only an LFCLK present, if again, the input is not changing (DC input). During times that they expect the input to change, they could enable SYSOSC.

Is it possible to use the OPAs with a DC input while the SYSOSC is disabled?

The clock requirements section for the OPA seems to suggest that the SYSOSC only needs to be active for chopping and rail-to-rail input. However, it does not explicitly state that if we turn off these features and the SYSOSC, the OPAs would still function.

Ideally, we would like the option to integrate your suggestion for working around the sleep2 issue("Before transitioning to sleep with the __WFI() call, switch the MCLK to LFCLK source. Then when you wake-up, switch the MCLK back to SYSOSC source.") with operational OPAs in cases where we wouldn't need RRI. Once again, the SYSOSC would be enabled in run when we are changing the OPA input, and when we go to sleep and the input is stable, the SYSOSC would be disabled.

If we need RRI, we would run the SYSOSC at 4MHz during sleep.

My initial thought was that VBOOST might be a limitation. However, upon reading the appropriate TRM section, it looks to me like VBOOST can operate off of the LFCLK.

Thanks,

Stuart