Tool/software:

I have a TM4C129ENCPDT processor running at 60MHz sampling voltage form a lead acid battery and the sample is very spiky.

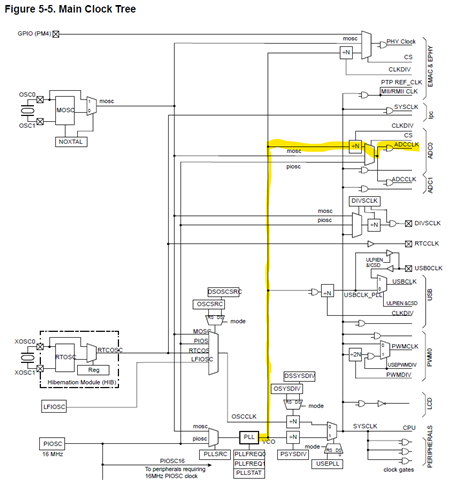

I am using a precision 3V reference, and running the ADC clock at 15MHz.

Enabling hardware oversampling or increasing the Sample Hold period seems to make very little difference.

Below is the capture of default sample settings with 15MHz sample clock and no hardware over sample in blue, followed by sample of same waveform with 32 hardware samples in Orange.

If I connect an external arduino processor to the same voltage, I get a clean waveform, see the blue waveform below.

I added some code to allow me to specify the ADC clock and calculate an appropriate divisor from my system clock of 60MHZ

ADCdivisor = ui32SysClock / ADC_CLK_SPEED;

ADCrate = ADC_CLOCK_RATE_FULL;

ADCclock = ui32SysClock / ADCdivisor;

if (ADCdivisor > 64)

{

ADCrate = ADC_CLOCK_RATE_HALF;

ADCdivisor = ui32SysClock / ADC_CLK_SPEED / 2;

ADCclock = ui32SysClock / ADCdivisor / 2;

if (ADCdivisor > 64)

{

ADCrate = ADC_CLOCK_RATE_FOURTH;

ADCdivisor = ui32SysClock / ADC_CLK_SPEED / 4;

ADCclock = ui32SysClock / ADCdivisor / 4;

if (ADCdivisor > 64)

{

ADCrate = ADC_CLOCK_RATE_EIGHTH;

ADCdivisor = ui32SysClock / ADC_CLK_SPEED / 8;

if (ADCdivisor > 64)

{

ADCdivisor = 64;

}

ADCclock = ui32SysClock / ADCdivisor / 8;

}

}

}

else if (ADCdivisor == 0)

{

ADCdivisor = 1;

ADCclock = ui32SysClock;

}

rprintf("Sysclock %d Divisor %d ADC Clock %d\r\n", ui32SysClock, ADCdivisor, ADCclock);

// ADC Clock can only be set on

ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADCrate, ADCdivisor);

ADC Initialisation is

// Initialisation ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADCrate, ADCdivisor); ADCHardwareOversampleConfigure(ADC0_BASE, 32); ADCSequenceDisable(ADC0_BASE, 1); ADCSequenceConfigure(ADC0_BASE, 1, ADC_TRIGGER_PROCESSOR, 0); ADCSequenceStepConfigure(ADC0_BASE, 1, 0, ADC_CTL_CH13 | ADC_CTL_IE | ADC_CTL_END); // Battery Volts ADCSequenceEnable(ADC0_BASE, 1); //Enable the ADC

Sample loop repeats the following:

ADCIntClear(ADC0_BASE, 1); //Clear Interrupt to proceed to next data capture

ADCProcessorTrigger(ADC0_BASE, 1); //Ask processor to trigger ADC

if (ADCIntStatus(ADC0_BASE, 1, false))

{

ADCSequenceDataGet(ADC0_BASE, 1, RawAnalogOther);

}

I have tried just changing one parameter at a time, but don't see any improvement to the spikes.

I am applying sample and hold as follows:

ADCSequenceStepConfigure(ADC0_BASE, 1, 0, ADC_CTL_CH13 | ADC_CTL_SHOLD_16);

ADCHardwareOversampleConfigure(ADC0_BASE, 32);

Hardware Oversample 0...64 gives little difference

ADC_CTL_SHOLD 2...256 makes very little difference.

Clock speed from 1MHz to 10MHz makes very little difference.

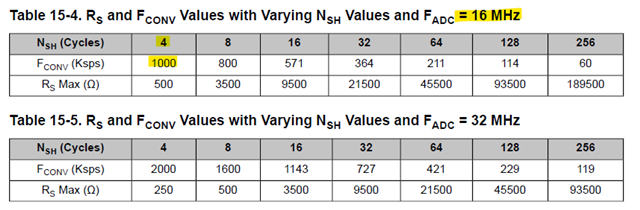

Interesting thing is that when I set 15MHz or above for the clock, my voltage output drops from 910 to 524, which seems to indicate the sample hold time is not long enough.

However, the voltage stays at this half level for sample hold time of 4 clocks or sample hold time of 256 clocks, no matter what sample hold time I use, the voltage remains at half level.

Change clock down to 10MHz and voltage is correct even with sample hold time of 4 clocks.

It looks like sample hold is not applied.

Any suggestion how I can improve the output?