Other Parts Discussed in Thread: HALCOGEN

Tool/software:

Using Auto ECC generation from CCS while programming in both Debug and Release builds. default .cmd linker file from halcogen.

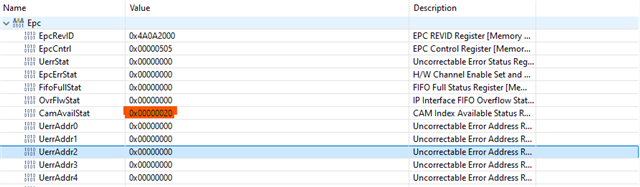

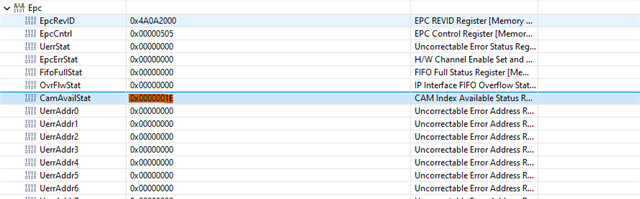

In Debug session on a debug build, i can see all the CAM entries are available. Error Pin Key status is 0x1H indicating no errors.

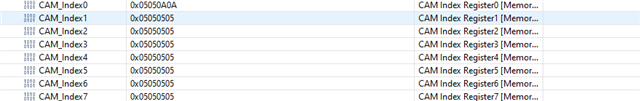

In Debug session on a release build, i can see 2 CAM entries are occupied, Error Pin Key status is 0x0H indicating errors on ECC validation.

CAM entries.

Questions are as follows:

1. How is this behavior different from Debug and Release builds ?

2. `The write data is masked with byten and stored into CAM on each index.` of 12.4.9 CAM Content Update Register n (CAM_CONTENT), i am having trouble comprehending what this statement means.

Thanks in advance