Part Number: AM2632

Tool/software:

Hi,

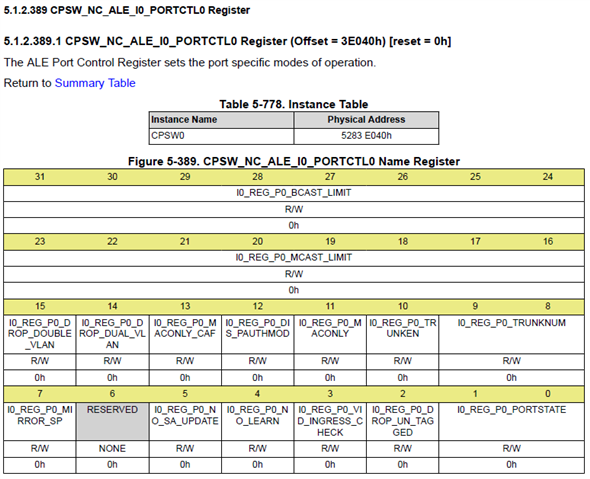

I have AM263x launchpad. I am using AM263x Sitara Processors Technical Reference Manual Register Addendum (Rev. E)

I was going through the enet (MAC) loopback example in mcu_plus_sdk_am263x_09_02_00_56 SDK for debugging the receive issue in my bare metal CPSW driver.

I noticed that port control register exists for Port 0 in AM263x Register Addendum (Rev E), but the port control register for Port 1 and Port 2 is missing.

Please share the information of the port control register for Port 1 and Port 2 of CPSW. Also, if there are any other missing registers in AM263x Register Addendum (Rev E) then please share information on them as well.

Thank you,

Shitanshu Desai