Part Number: AM263P4-Q1

Other Parts Discussed in Thread: TIDM-02018, SYSCONFIG

Tool/software:

Hi,

I am fairly new to the AM263P4-Q1 and working myself into an existing project.

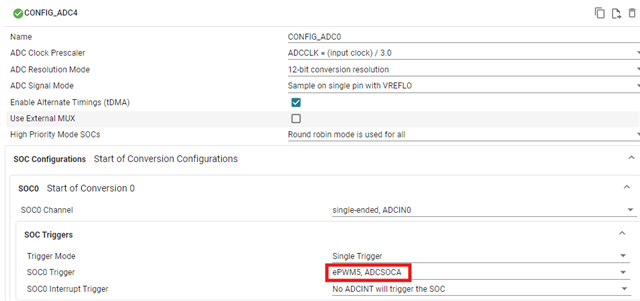

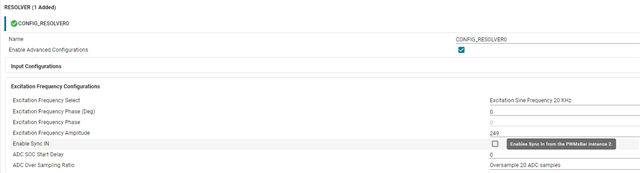

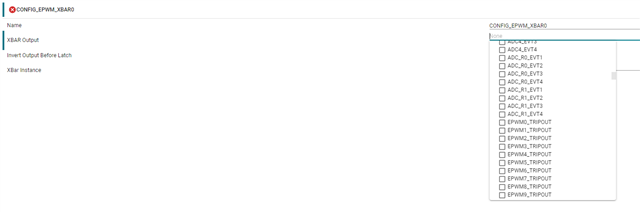

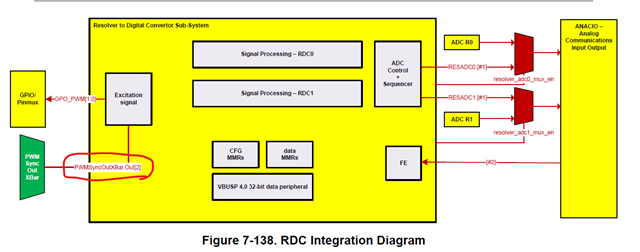

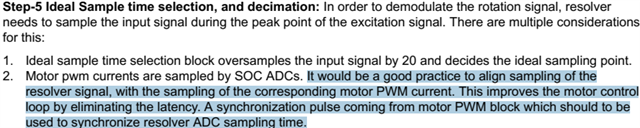

As stated in the title I want to synchronize the resolver signal sampling with the motor PWM current sampling as proposed in the technical reference manual 7.5.3.1.6 - Step 5.2:

Is there any guideline how to do as proposed in the last sentence marked: "A synchronization pulse coming from motor PWM block which should to be used to synchronize resolver ADC sampling time." ?

Best regards

Norbert