Part Number: AM263P4

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

I have a working multicore project that, when I load it with CCS in devboot mode, works just fine. MCAN baudrate is and should be 1000 kbit/s.

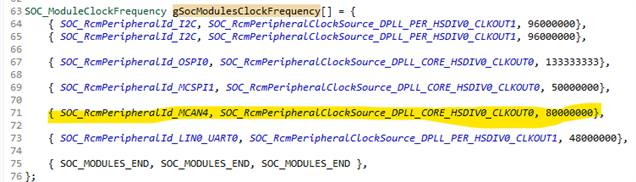

However, when this project gets loaded from flash via SBL in OSPI boot mode, the baudrate is wrong with about 310 kbit/s.

- What could be the problem here?

- When loading with CCS the GEL-files do a lot of clock configurations. Where/When does this happen when booting via SBL? Do I have to do some additional config in my SBL?

Additional info:

SOC: AM263P4_ZCZ_F

MCAN code mostly from 'mcan_external_read_write' example

SBL code mostly from 'sbl_ospi' example

Best regards,

Frank