Tool/software:

Hello,

we have integrated the MSPM0G3507-Q1 for a custom design. We added a 24 MHz external Crystal (load capacitance 8 pF --> we use 12 pF capacitance on XTAL). We verified the crystal with the scope and its in the specified tolerance range.

We got some samples and flashed these with our SW. Our SW creates a simple PWM Timer with a clock of 5 MHz. If the PCB gets hotter then the clock gets more instable (PLL active), the timer clock fluctuates around some khz and thats not in the tolerance range.

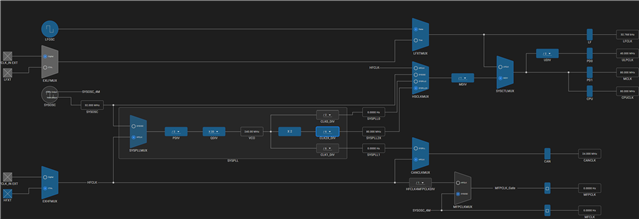

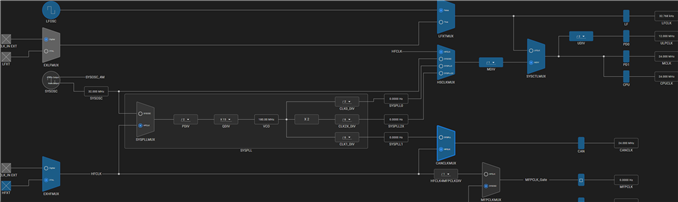

Originally Clock tree configuration

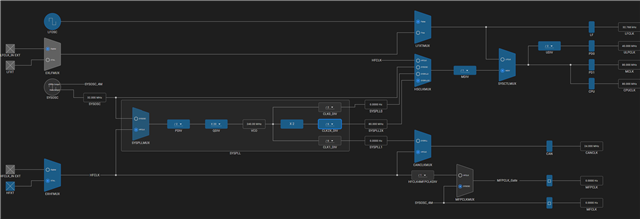

I made some tests and I used a simple example GPIO_toggle_output and modfified this. I just modified the Clock tree and added a pwm timer with 5 MHz, no gpio pins are toggling.

The aim was to identifiy the origin of the instability, I made 4 tries:

First try:

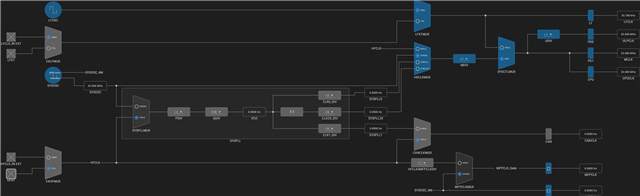

Only usage of internal Clock SOSC with this Clock tree configuration

--> 4 MHz clock output stable

Second try:

Only usage of internal Clock SOSC with PLL active

-->4 MHz clock ist not stable when PLL is active--> It's probably due to the PLL

Third try:

External 24 MHz Crystal without PLL--> 4MHz clock output stable

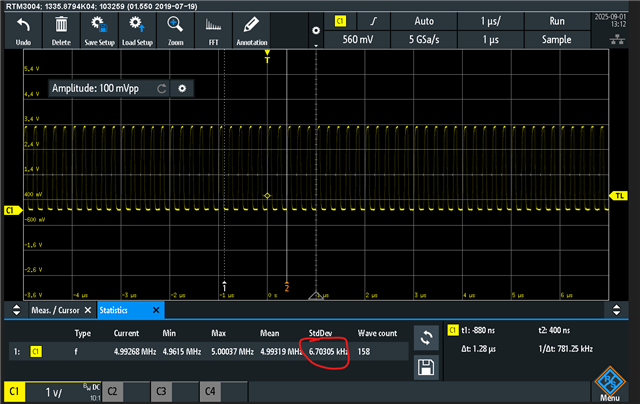

Fourth Try:

External 24 MHz Crystal with PLL (original clock tree)--> 5MHz clock outptut not stable

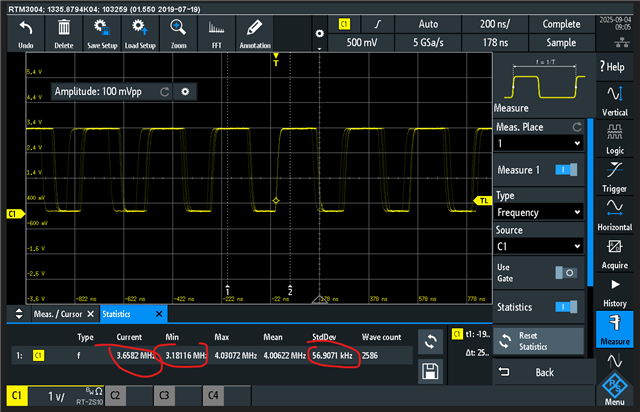

Picture from scope (std deviation >6 kHz increases until 30 kHz)

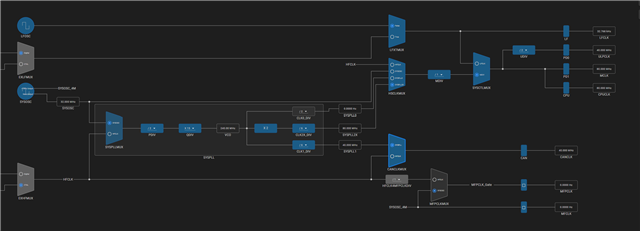

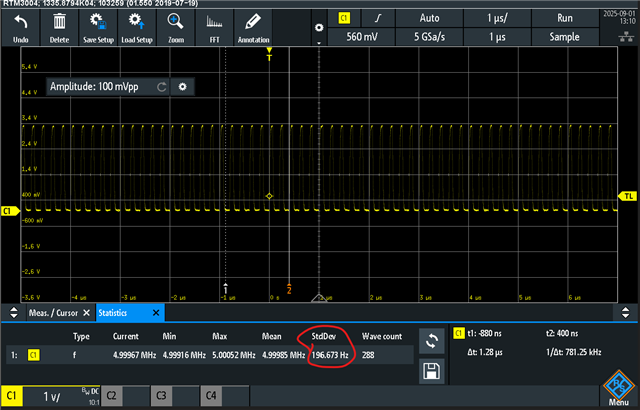

If i reduce enlarge the clk2x_Div from 6 to 8 --> CPU_CLK has

60 MHz instead of 80 MHz --> output clock of timer (5 MHz) is also stable!

scope picture (std deviation <200 Hz)

So it seems that there is a problem with PLL configuration.

In SYSCTL "Enable Check for Clock Stabilization" is always on. We use CCS 20.0 but it doesn't matter which version we use. We have also samples where we have no problems with the 80 MHz output PLL configuration.

We are not sure if some of our MCUs has a temperature problem, a soldering problem is not visible. Sometimes we change the IC and then it works with the original configuration. Is there any known problem with PLL config or clock config or timer config, which can cause a unstable clock with a temperature increase (any prescaling settings or something else)?