Tool/software:

Dear TI Support Team,

I am working with the MSP432E4 MCU and attempting to generate a PWM signal on PF1 (M0PWM1). The PF1 pin is connected to an FPGA on the other side, where the PWM output will be used as a reference clock.

I have configured the system clock to 120 MHz using the PLL and enabled PWM0. The PF1 pin is configured as GPIO_PF1_M0PWM1, and I am using PWM Generator 0, Output 1. My code is based on TI’s driverlib, and I followed the standard initialization steps:

-

System clock set to 120 MHz

-

SysCtlPeripheralEnable()for GPIOF and PWM0 -

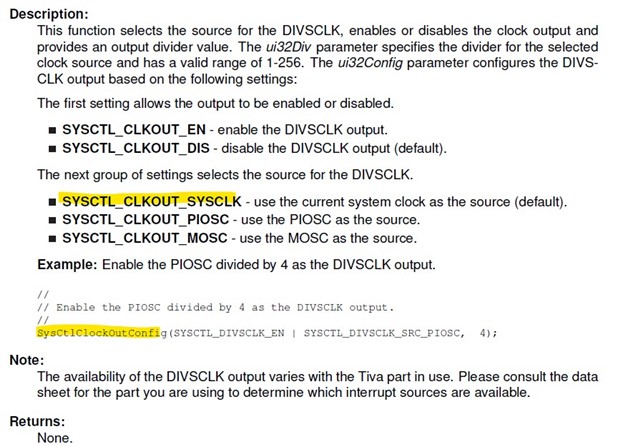

SysCtlPWMClockSet(SYSCTL_PWMDIV_1)for maximum PWM resolution -

PF1 configured using

GPIOPinConfigure(GPIO_PF1_M0PWM1)andGPIOPinTypePWM() -

PWMGenConfigure(PWM0_BASE, PWM_GEN_0, PWM_GEN_MODE_DOWN) -

PWMGenPeriodSet()andPWMPulseWidthSet()used to configure period and duty cycle -

PWMOutputState()andPWMGenEnable()called

However, I am observing that PF1 remains always high or if i change anything i could not see any output in the PF1 Pin. Even when I configure for a low frequency (e.g., 1 kHz with 50% duty cycle), I do not see the expected waveform.

Could you please clarify the following points?

-

Is there any additional configuration required for M0PWM1 (PF1) output?

-

Are there known limitations on maximum PWM frequency achievable on PF1?

-

Could there be any restriction when driving an FPGA input directly from the PWM pin?

Here below i am giving my code for your reference,

#include <stdint.h>

#include <stdbool.h>

#include "ti/devices/msp432e4/driverlib/driverlib.h"

#define SYSTEM_CLOCK_HZ 120000000 // 120 MHz system clock

#define PWM_FREQUENCY 1000 // 1 kHz for easy observation

#define PWM_DUTY_PERCENT 50 // 50% duty cycle

uint32_t ui32SysClock;

uint32_t ui32Period;

// 1. Configure system clock for 120 MHz using PLL

ui32SysClock = SysCtlClockFreqSet(

(SYSCTL_XTAL_25MHZ |

SYSCTL_OSC_MAIN |

SYSCTL_USE_PLL |

SYSCTL_CFG_VCO_480),

SYSTEM_CLOCK_HZ);

// 2. Enable peripherals

SysCtlPeripheralEnable(SYSCTL_PERIPH_PWM0);

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOF);

while(!SysCtlPeripheralReady(SYSCTL_PERIPH_PWM0));

while(!SysCtlPeripheralReady(SYSCTL_PERIPH_GPIOF));

// 3. Configure PF1 as M0PWM1

GPIOPinConfigure(GPIO_PF1_M0PWM1);

GPIOPinTypePWM(GPIO_PORTF_BASE, GPIO_PIN_1);

// 4. Disable generator before configuration

PWMGenDisable(PWM0_BASE, PWM_GEN_0);

// Configure generator 0 for down-count mode

PWMGenConfigure(PWM0_BASE, PWM_GEN_0, PWM_GEN_MODE_DOWN);

// 5. Set PWM period and duty cycle

ui32Period = (ui32SysClock / PWM_FREQUENCY);

PWMGenPeriodSet(PWM0_BASE, PWM_GEN_0, ui32Period);

// Set duty cycle = 50%

PWMPulseWidthSet(PWM0_BASE, PWM_OUT_1, (ui32Period * PWM_DUTY_PERCENT) / 100);

// 6. Enable PWM output

PWMOutputState(PWM0_BASE, PWM_OUT_1_BIT, true);

// Enable generator

PWMGenEnable(PWM0_BASE, PWM_GEN_0);

while(1)

{

// Loop forever – PWM runs in hardware

}

I would appreciate your guidance in resolving this issue, as PF1 output is crucial for my design.

Regards,

J.Manikandasamy