Tool/software:

Hi Team,

I am working with the MSPM0 and trying to connect it to an SBC (TCAN284X devices) via the SPI bus.

I have everything pretty much working - but I can't find a flag or register where I can modify the behavior of the nCS pin.

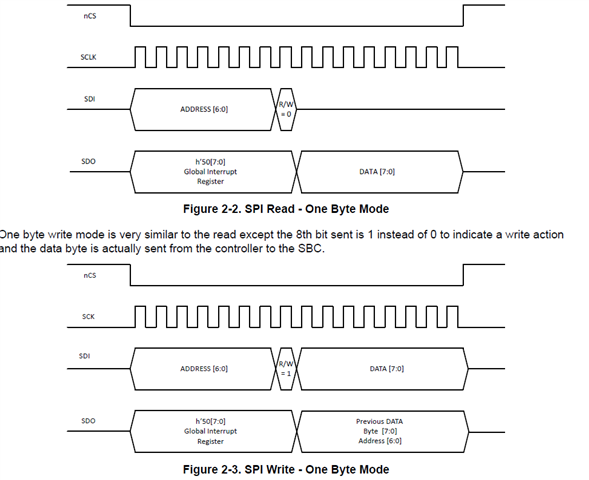

Currently the device will send the 7 bit address + r/w bit and then raise the nCS pin high before bringing it back low to send the 8-bit transaction or receive the 8-bit message.

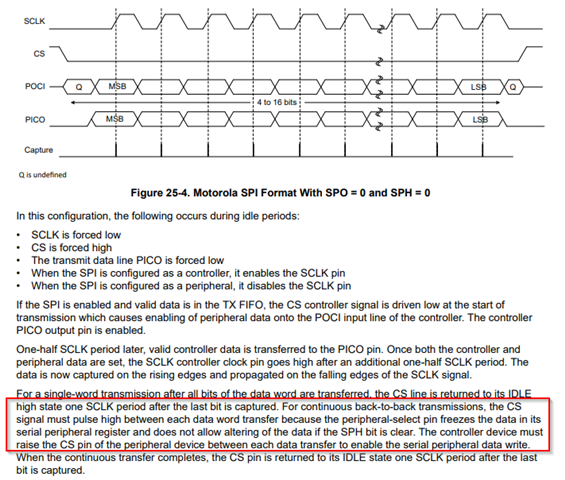

The SBC expects nCS to be low for the entire trasaction - including address and data - like below:

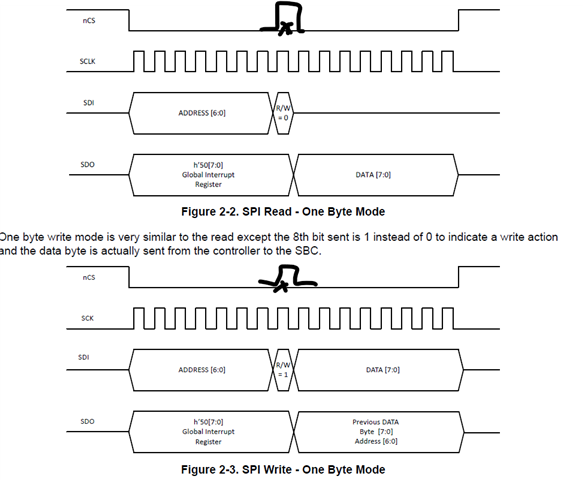

But the nCS pin on the MCU keeps doing this:

Where it pulls nCS high after every byte.

I believe there should be a way to fix this where the entire transaction has nCS low instead of going low for each byte. As with what is currently happening now is that the SPI bus on the SBC gets reset everytime the nCS pin goes high in the middle of a transition.

I tried just using a GPIO as nCS but the timing didn't look good and the output characteristics of the GPIO were not great in terms of how it looked - I am using the launchpad so it is a bit limited in all the pins I can access.

So my main questions are:

1. Can I ensure that nCS is low for the entire transaction instead of just 1 byte (I have tried using 16bit transactions - but that also didn't seem to work)

2. If I can do point 1 - how do I do that.

Any help is greatly appreciated - we want to use MSPM0's as companion MCU's for a lot of our SBCs due to the CAN controller so this ask would help us not only with this problem but help us solidify a companion MCU with this device.

Best,

Parker Dodson