Other Parts Discussed in Thread: TMDS243EVM

Tool/software:

Hello,

I am working with [enet_layer2_icssg] which I modified for EtherCAT communication experiments.

In this project, I've created a transmit task that calls EnetDma_submitTxPktQ three times every 500us to send an Ethercat frame three times,

and a receive task that, upon receiving the returned frame, uses uDMA to DMA transfer the received data to another memory location.

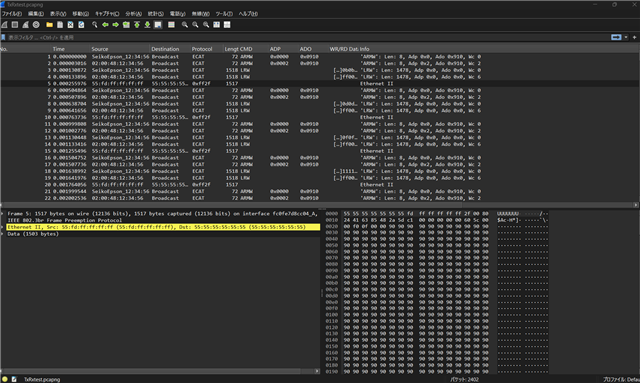

During this process, the receive task occasionally pauses for approximately 350ms, anywhere from a few minutes to an hour.

When this occurs, it always lasts for approximately 348-352ms, giving the impression that something is controlling it.

(The transmit task continues to run during this pause.)

Looking more closely at the phenomenon, it appears that no receive interrupts are received during this approximately 350ms period, leading me to suspect that the frame itself may be deleted due to a CRC error or similar.

I'd like to identify the cause of this behavior, so I'd appreciate any information that could provide a clue.

For example, EnetDma_submitTxPktQ should not be called again until the frame has been completely transmitted.

Supplementary Note

When sending three frames, the first one is sent, followed by the second and third ones a short time later.

EnetDma_submitTxPktQ is called at the following timings: first frame → 100us has elapsed → second frame → third frame.

Also, if the second and third frames are sent simultaneously using EnetQueue_enq, this issue has not yet occurred. (I've run it for about 16 hours.)

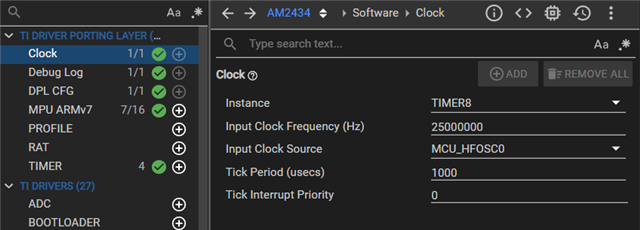

SDK mcu_plus_sdk_am243x_11_00_00_15

Board used AM243xEVM / Custom Board (AM2432)

Board has one ICSSG port connected to the slave and the other is disconnected

Configuration: AM2432(ethercat master) - profishark1G(LAN analyzer) - AM2432(ethercat slave1) - AM2432(ethercat slave2)