Tool/software:

Hello,

we are using the DWWD on the Sitara.

Our application is pretty simple: We have a task and the watchdog. The task clears the watchdog in a period that is shorter than the period of the watchdog. So the trigger does never occur.

The watchdog is deactivated for debug-builds and activated for release builds. If we want to debug a release-build we run into some problems since the watchdog triggers in some scenarios:

if a release-build is already on the device and a release-build is loaded via CCS: Watchdog triggers immediataley after Watchdog_clear()

if a debug-build is already on the device and a release-build is loaded first via CCS: works.

if afterwards a a release-build is loaded again: Watchdog triggers immediately.

So it seems that if the Watchdog is configured once, it will directly trigger and I do not know why.

We also wrote our own Watchdog driver which utilizes the watchdog-functionality but I oriented at the examples and the TRM. The only thing I did contrary to the examples is the clear, since the TRM says:

"The RTI_INTR_WWD interrupt handler needs to clear the watchdog violation status flag(s) and then service the watchdog by writing the correct sequence in the watchdog key RTI_WDKEY register"

But the examples did it the other way round. nevertheless the order, the problem persists.

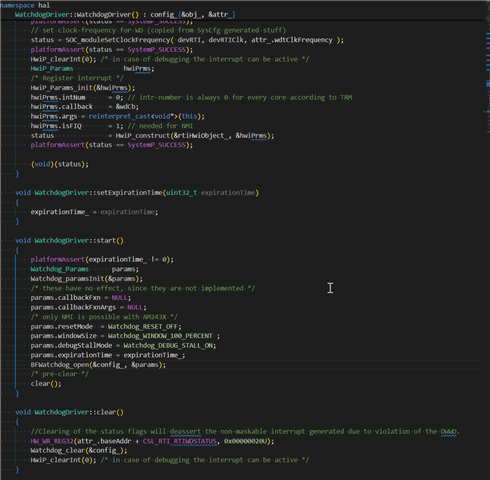

In general we could say that this is the code that is used for our watchdog:

The BFWatchdog_open is the same as the Watchdog_open, except it does not take an array index but the config itself.

We also use it as an fiq-interrupt, because we noticed a HwiP_disable also would block the watchdog-interrupt, which it shouldn't and nmi is not available that way on the am243x:

We use the watchdog instance 8, so TISCI_DEV_RTI8/WATCHDOG_INST_ID_8 on the mcu0_0. and the 9 corresponding on the mcu0_1.

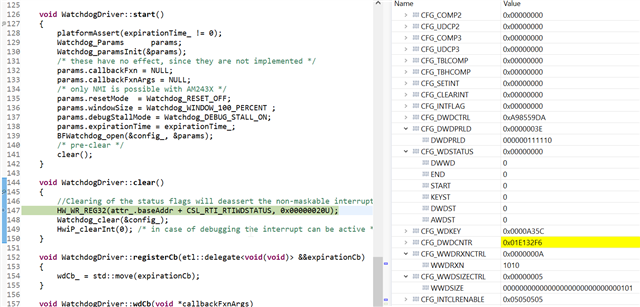

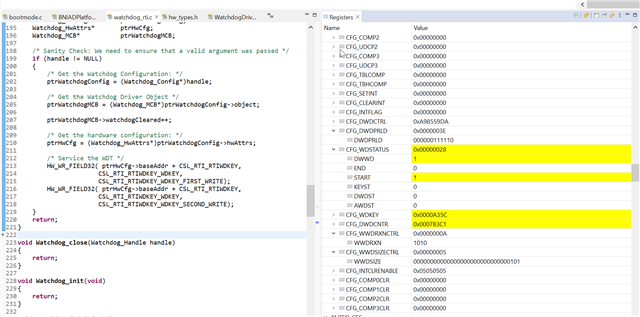

so, if we have a release-build already on the device, we come here:

WDSTATUS looks nice.

And now as soon as the Watchdog_clear is returning:

The WDSTATUS somehow gets set?

CCS does not use the v1-file, but the v0, that's why the line does not match the code on the left.

But we always experience that and that makes it impossible to debug a board which has a release-firmware already on it. So, a firmware which already initialized the Watchdog once.

Also our watchdog-period is set to 16 seconds! So it's not like I were in a breakpoint for too long or smth. it immediately occurs after start as soon as the Watchdog is created.

Is there something else that is not documented or I did just read over, which needs to be done to make this work?

This is really needed to be able to debug our release-firmware in some cases. and with that it's just not possible.

Best regards

Felix